The thought of an interview can be nerve-wracking, but the right preparation can make all the difference. Explore this comprehensive guide to IC Design interview questions and gain the confidence you need to showcase your abilities and secure the role.

Questions Asked in IC Design Interview

Q 1. Explain the difference between CMOS and NMOS technologies.

CMOS (Complementary Metal-Oxide-Semiconductor) and NMOS (N-type Metal-Oxide-Semiconductor) are two fundamental technologies used in integrated circuit (IC) design. The key difference lies in their transistor structures and how they operate. NMOS technology uses only N-type transistors, while CMOS technology utilizes both N-type and P-type transistors in a complementary fashion.

NMOS circuits are simpler to fabricate, but consume more power due to the continuous current flow when the transistor is ON. Imagine a simple switch: in NMOS, the switch is always slightly leaky even when ‘off’.

CMOS circuits, on the other hand, offer significantly lower power consumption. This is because, in a CMOS inverter for example, only one transistor is ON at any given time. Think of it as a highly efficient double-switch mechanism: only one switch is ever conducting. This complementary structure makes CMOS the dominant technology in modern IC design, especially for low-power applications like mobile devices.

In short: NMOS is simpler but power-hungry; CMOS is more complex but highly power-efficient.

Q 2. Describe the process of designing a digital circuit using Verilog or VHDL.

Designing a digital circuit using Verilog or VHDL involves a structured process. Both are Hardware Description Languages (HDLs) that allow you to describe the functionality and behavior of a digital circuit using a textual representation, rather than drawing schematics.

- Design Entry: Start with specifying the circuit’s functionality in the chosen HDL (Verilog or VHDL). This often involves writing behavioral, RTL (Register-Transfer Level), or gate-level descriptions. For instance, you might describe a simple adder using behavioral descriptions, then refine it to RTL level for synthesizability.

- Simulation and Verification: Use a simulator (like ModelSim or QuestaSim) to test your design’s functionality. You’ll write testbenches to apply various inputs and verify the outputs match the expected behavior. This helps catch bugs early in the design process.

- Synthesis: Employ a synthesis tool (like Synopsys Design Compiler) to translate the HDL code into a netlist, which is a representation of the circuit in terms of logic gates. The synthesis tool optimizes the design based on constraints like timing and area. Here you specify constraints for clock speed, power, and area.

- Physical Design: This stage focuses on placing and routing the logic gates on the silicon die. Tools like Innovus or Cadence Allegro are used to optimize for timing, area, and power. The netlist is transformed into a layout, which is a physical representation of the circuit.

- Verification (Post-Layout): After the physical design, you’ll need to perform post-layout simulations to verify that the timing and functionality are still correct. This usually involves Static Timing Analysis (STA) to ensure the circuit meets timing requirements.

- Fabrication (Tape-Out): Once verification is complete, the layout is sent to a fabrication facility for manufacturing.

Example (Verilog): A simple AND gate:

module and_gate (input a, input b, output y); assign y = a & b; endmodule;Q 3. What are the key challenges in high-speed digital IC design?

High-speed digital IC design presents several formidable challenges:

- Signal Integrity: At high speeds, signal reflections, crosstalk, and electromagnetic interference (EMI) become significant issues. These can lead to signal degradation and timing violations.

- Power Consumption: Higher clock speeds demand more power, leading to heat dissipation problems. This necessitates efficient power management techniques.

- Timing Closure: Meeting timing constraints becomes increasingly difficult as clock frequencies increase. This involves careful optimization of the design and physical layout.

- Interconnect Delay: The time it takes for signals to travel between different parts of the chip becomes a dominant factor at high speeds. Efficient routing and careful placement are crucial.

- Electromagnetic Interference (EMI): High-speed signals can radiate significant EMI, which can interfere with other components on the chip or even nearby devices. Shielding and careful layout are needed to mitigate this.

Think of it like a high-speed highway system. At slow speeds, you only worry about the cars’ performance. At high speeds, you need to manage traffic flow, ensure roads are smooth to prevent accidents (signal degradation), manage traffic lights (timing closure), and consider road construction to reduce travel time (interconnect delay).

Q 4. How do you perform static timing analysis (STA)?

Static Timing Analysis (STA) is a crucial step in verifying the timing behavior of a digital circuit. It’s a static analysis (meaning it doesn’t involve simulating the circuit’s dynamic behavior) that checks if the circuit meets its timing constraints.

Process:

- Delay Calculation: STA tools use the netlist and library information (which contains delay information for each logic gate) to calculate the propagation delays along each path in the circuit.

- Constraint Definition: The designer specifies timing constraints, such as clock frequency, setup and hold times for flip-flops, and maximum delays for signals. These constraints define the acceptable timing behavior.

- Path Analysis: The tool analyzes all possible paths in the circuit, from clock source to flip-flop inputs or other timing-critical nodes.

- Timing Violation Detection: STA identifies any timing violations, such as setup time violations (data arrives too late) or hold time violations (data arrives too early). It reports the severity and location of these violations.

- Optimization and Iteration: Based on the STA results, the designer may need to make changes to the design or the physical layout to fix any timing violations. This is an iterative process until the design meets all timing constraints.

Example: A flip-flop with a setup time constraint of 1 ns and a clock period of 10 ns would fail STA if the propagation delay of the logic driving its input exceeds 9 ns (10 ns – 1 ns).

Q 5. Explain the concept of metastability in digital circuits.

Metastability is a critical issue in digital circuits where a flip-flop’s output remains in an unpredictable state for an indeterminate amount of time. This happens when the input signal changes close to the clock edge, making the flip-flop unable to reliably sample the input. Think of it like a coin spinning in the air – it’s neither heads nor tails until it lands.

Causes: Metastability occurs when the setup and hold time requirements of a flip-flop are not met. This is especially common when asynchronous signals are sampled by a synchronous circuit.

Mitigation: Metastability cannot be completely eliminated, but its probability can be significantly reduced by:

- Asynchronous signal synchronization: Using multi-stage synchronizers to filter asynchronous inputs. Each stage increases the probability of resolving metastability before the signal reaches the critical path.

- Sufficient setup/hold times: Designing the circuit to provide enough time for the flip-flops to settle reliably.

- Careful clock distribution: Ensuring a clean and stable clock signal to all flip-flops.

Metastability is a probabilistic phenomenon; it’s not a guaranteed failure, but a risk that needs careful management.

Q 6. What are different types of power optimization techniques used in IC design?

Power optimization is paramount in modern IC design, especially for mobile and battery-powered devices. Various techniques are employed to minimize power consumption:

- Clock Gating: Disabling the clock signal to inactive parts of the circuit, reducing power dissipation during idle periods.

- Power Gating: Completely isolating sections of the circuit by turning off the power supply when not needed.

- Voltage Scaling: Reducing the operating voltage of the circuit, which significantly reduces power consumption (P ∝ V²).

- Low-Power Design Styles: Utilizing specific design styles, like multi-threshold CMOS (MTCMOS), that reduce power consumption at the transistor level.

- Design Optimization: Reducing logic complexity and optimizing the circuit’s architecture to minimize power dissipation. This might involve careful gate sizing, using efficient logic structures, or employing techniques such as pipelining to improve throughput while maintaining reasonable power needs.

- Process Technology: Choosing a process technology node (e.g., 7nm, 5nm) optimized for lower power consumption.

Power optimization is a multifaceted problem. It’s not just about choosing the right components but also applying smart architectural and design choices to minimise energy use, with each technique impacting the overall performance differently. For instance, while clock gating might help reduce average power, aggressive voltage scaling could impact timing and necessitate careful consideration of other aspects like margins.

Q 7. Describe your experience with different synthesis tools (e.g., Synopsys Design Compiler).

I have extensive experience using Synopsys Design Compiler, a leading synthesis tool in the IC design industry. I’ve utilized it throughout the entire design flow, from RTL synthesis to generating optimized netlists for subsequent physical design stages. My expertise encompasses various aspects:

- RTL Synthesis: Successfully synthesized complex designs, utilizing Design Compiler’s optimization capabilities to achieve the desired area, timing, and power targets. This often involves manipulating constraints to get the optimal balance.

- Constraint Management: Developed and refined timing constraints (clock period, setup/hold times) to ensure the circuit meets specifications. This requires a deep understanding of circuit behavior and interactions between different parts of the design.

- Script Writing (Tcl): Leveraged Tcl scripting extensively to automate the synthesis process, improve efficiency, and facilitate design iterations. This is especially useful for large and complex projects.

- Power Optimization: Used Design Compiler’s power analysis and optimization features to minimize power dissipation, and experimented with different synthesis strategies like multi-voltage synthesis. This requires a keen understanding of different power analysis techniques and how they impact circuit design.

- Library Selection and Characterization: Worked with different standard cell libraries, understanding the tradeoffs between area, speed, and power for various libraries and using characterization tools to extract delay models.

I’ve successfully applied these skills to diverse projects, consistently delivering high-quality, optimized designs. For example, in one project, I used Design Compiler’s advanced optimization capabilities to reduce power consumption by 15% without compromising performance.

Q 8. How do you ensure the testability of your IC designs?

Ensuring testability in IC design is paramount. It’s like building a house – you wouldn’t construct it without considering how you’ll inspect its structural integrity. We employ several strategies to achieve this. First, design for testability (DFT) techniques are crucial. This involves adding extra circuitry specifically for testing purposes. Common DFT methods include:

- Scan chain design: This allows us to serially access and control the internal flip-flops of the circuit, enabling comprehensive testing.

- Built-in self-test (BIST): This incorporates test pattern generation and response analysis directly within the chip, reducing reliance on external test equipment.

- Boundary scan (JTAG): This standardized interface allows access to the chip’s inputs and outputs for testing.

Secondly, we use fault simulation. We inject various faults (e.g., stuck-at-0, stuck-at-1, bridging faults) into a simulation model of the design to determine if our test vectors effectively detect them. This helps us refine our test strategy and ensure high fault coverage. Finally, we employ at-speed testing to verify functionality under actual operating conditions, ensuring the chip performs correctly under stress. For example, in a high-speed data converter, we’d verify the signal integrity and data accuracy at the target clock frequency.

Q 9. Explain the different types of memory in IC design.

Memory in IC design is broadly categorized into several types, each with its own strengths and weaknesses. Think of it like having different types of storage in your computer: RAM for fast access, hard drive for bulk storage, etc.

- SRAM (Static Random Access Memory): This is fast and uses flip-flops to store data. It retains data as long as power is supplied. It’s ideal for cache memory in CPUs.

- DRAM (Dynamic Random Access Memory): This is denser and cheaper than SRAM but requires constant refreshing to retain data because it stores information as charge in a capacitor. It’s commonly used for main memory (system RAM).

- ROM (Read-Only Memory): Data is permanently stored during fabrication and cannot be altered. Used for storing firmware or boot code.

- Flash Memory: This is non-volatile (retains data even when power is off) and can be reprogrammed, although slower than SRAM or DRAM. Used in solid-state drives (SSDs) and embedded systems.

- EEPROM (Electrically Erasable Programmable Read-Only Memory): Similar to flash memory, but individual bytes can be erased and reprogrammed, offering more flexibility than ROM.

The choice of memory type depends on factors like speed requirements, cost, power consumption, and the application’s need for data persistence.

Q 10. What are your experiences with different layout tools (e.g., Cadence Virtuoso)?

I have extensive experience with Cadence Virtuoso, a leading layout tool in IC design. It’s like having a sophisticated CAD program specifically tailored for designing the intricate physical layout of integrated circuits. My expertise spans various aspects, including schematic capture, layout design, physical verification (DRC, LVS), and parasitic extraction. I’ve used it to design complex analog and mixed-signal ICs. For instance, I’ve used Virtuoso to design the layout of a high-speed ADC, meticulously ensuring proper routing and placement to minimize noise and signal interference. The tool’s capabilities in handling complex layouts, coupled with its advanced simulation features, make it indispensable for ensuring design quality and performance.

Beyond Virtuoso, I’ve also worked with other layout tools like Synopsys IC Compiler for digital design and have a working knowledge of other EDA (Electronic Design Automation) software like Mentor Graphics.

Q 11. How do you handle signal integrity issues in high-speed designs?

Signal integrity in high-speed designs is critical – think of it as maintaining a clear and undistorted signal throughout the chip. Issues like reflections, crosstalk, and jitter can significantly affect performance and functionality. We address these using a multi-pronged approach:

- Careful Signal Routing: We use controlled impedance traces, shielding, and proper grounding techniques to minimize reflections and crosstalk.

- Termination Techniques: Using series and parallel termination resistors at the end of transmission lines helps to absorb reflections and prevent signal distortions.

- Simulation and Analysis: We employ advanced electromagnetic field (EMF) simulations (e.g., using tools like HFSS or ADS) to predict and mitigate signal integrity problems before fabrication.

- Decoupling Capacitors: These are strategically placed to minimize noise and voltage fluctuations on power supply lines.

For example, in a high-speed serial link design, careful control of impedance matching is essential to minimize signal reflections and ensure data integrity. Failure to address signal integrity issues can lead to data errors, reduced performance, or even complete system failure.

Q 12. Explain your understanding of clock domain crossing.

Clock domain crossing (CDC) refers to the situation where data is transferred between different clock domains within an IC. This is a common scenario in complex designs, but it presents challenges because asynchronous clock domains can lead to metastability – a condition where the data signal is neither a clear ‘0’ nor ‘1’.

Imagine two clocks ticking at slightly different rates. When data is transferred between them, there’s a risk the receiving clock domain might ‘catch’ the data in an unpredictable state. To mitigate this, we use several techniques:

- Synchronization Flip-Flops: A series of flip-flops in the receiving clock domain are used to sample the incoming data multiple times, increasing the probability of capturing a stable value.

- Asynchronous FIFOs (First-In, First-Out): These specialized FIFOs handle data transfer between asynchronous clock domains without requiring direct synchronization. They use handshaking signals to manage data flow.

- Gray Code Encoding: For certain types of data, Gray code encoding minimizes the number of bit changes between successive states, reducing the likelihood of metastability.

Careful consideration of CDC is essential to prevent data corruption and ensure the system’s reliability. Poorly handled CDC can lead to intermittent failures that are notoriously difficult to debug.

Q 13. Describe your experience with scripting languages like TCL or Perl in IC design.

Scripting languages like TCL and Perl are essential tools in IC design, automating repetitive tasks and increasing efficiency. It’s like having a personal assistant to handle the tedious parts of the design process, allowing engineers to focus on the more creative aspects. I’ve used TCL extensively within Cadence Virtuoso to automate layout tasks, such as generating and routing signals in a complex analog layout. For instance, I’ve written TCL scripts to automatically place components, route signals based on pre-defined rules, and perform design rule checks.

Perl’s strengths lie in its text-processing capabilities. I’ve used it to parse simulation results, extract key data, and generate reports. This is particularly helpful in identifying areas of potential concern or to validate the circuit’s performance against specifications. For example, I’ve used Perl to automatically analyze the results of thousands of simulations to detect any anomalies in the behavior of a specific circuit component.

Q 14. What are different types of analog filters and their applications?

Analog filters are essential components in many ICs, used to selectively pass or reject specific frequency ranges. Think of it like a sieve for frequencies, letting certain frequencies pass through while blocking others.

- Passive Filters: These are built using only resistors, capacitors, and inductors. They are simpler but often less flexible in terms of performance.

- Active Filters: These use operational amplifiers (op-amps) in addition to passive components. They offer greater flexibility in design, allowing for sharper cutoff frequencies and higher Q factors (a measure of a filter’s selectivity).

Common types include:

- Low-pass filters: Pass frequencies below a cutoff frequency and attenuate frequencies above it. Used in audio applications to remove high-frequency noise.

- High-pass filters: Pass frequencies above a cutoff frequency and attenuate frequencies below it. Used to remove low-frequency noise or DC components.

- Band-pass filters: Pass a specific range of frequencies and attenuate frequencies outside that range. Used in radio receivers to select a particular channel.

- Band-stop (notch) filters: Attenuate frequencies within a specific range and pass frequencies outside that range. Used to remove unwanted interference or noise at a specific frequency.

The choice of filter type and its design parameters (cutoff frequency, Q factor, etc.) depend on the specific application requirements.

Q 15. Explain your understanding of noise analysis in analog circuits.

Noise analysis in analog circuits is crucial for ensuring the proper functionality and reliability of a design. It involves identifying and quantifying various noise sources that can corrupt the signal, ultimately affecting the circuit’s performance. These sources can be internal, like thermal noise in resistors, or external, such as electromagnetic interference (EMI).

The process typically starts with identifying potential noise sources using circuit schematics and simulations. We then analyze how these sources propagate through the circuit, impacting signal integrity. Common techniques include:

- Calculating noise power spectral density (PSD): This tells us how much noise power is present at different frequencies.

- Using simulation tools like Spectre or Cadence Virtuoso: These tools allow for accurate noise simulations, providing insights into total integrated noise and other relevant metrics.

- Analyzing noise margins: This determines how much noise the circuit can tolerate before malfunctioning. Sufficient noise margin is critical for robust designs.

For example, in the design of an operational amplifier (op-amp), noise analysis is critical to ensure that the output signal isn’t significantly degraded by the inherent noise in the transistors and resistors. We might analyze the input-referred noise voltage to quantify the overall noise level of the op-amp. A high input-referred noise voltage would indicate a need for design optimization to reduce the noise contribution from each component.

Career Expert Tips:

- Ace those interviews! Prepare effectively by reviewing the Top 50 Most Common Interview Questions on ResumeGemini.

- Navigate your job search with confidence! Explore a wide range of Career Tips on ResumeGemini. Learn about common challenges and recommendations to overcome them.

- Craft the perfect resume! Master the Art of Resume Writing with ResumeGemini’s guide. Showcase your unique qualifications and achievements effectively.

- Don’t miss out on holiday savings! Build your dream resume with ResumeGemini’s ATS optimized templates.

Q 16. How do you design a low-power analog circuit?

Designing a low-power analog circuit requires a multi-faceted approach, focusing on minimizing power consumption at every stage. This involves careful consideration of circuit topology, component selection, and operating conditions. Key strategies include:

- Choosing low-power components: Using transistors with low leakage currents and optimizing the bias currents are crucial steps. We might select transistors with smaller gate lengths to reduce parasitic capacitances.

- Optimizing the biasing scheme: Reducing the supply voltage and adopting techniques like adaptive biasing can significantly reduce power. This often involves trade-offs with performance.

- Employing power-saving techniques: Techniques like clock gating, power gating, and using low-power operational amplifiers are essential. For example, clock gating can save significant power in parts of the circuit that are not actively processing data.

- Careful design of supply voltage regulators: These regulators must be highly efficient to avoid unnecessary power losses. Low-dropout (LDO) regulators are a common choice.

For example, in the design of a low-power sensor interface, we might use a sub-threshold design technique. This involves operating transistors at voltages significantly lower than their threshold voltage to reduce power consumption, although this comes at the cost of reduced speed.

Q 17. What are the key differences between ASIC and FPGA?

ASICs (Application-Specific Integrated Circuits) and FPGAs (Field-Programmable Gate Arrays) are both integrated circuits, but they differ significantly in their design, flexibility, and application.

- ASICs: These are custom-designed chips tailored for a specific application. They offer the highest performance and power efficiency but require a longer design cycle and higher upfront costs. They are ideal for high-volume applications where the cost of customization is offset by the production volume. Think of a specialized processor in a high-end smartphone.

- FPGAs: These are reconfigurable chips with a matrix of logic blocks and interconnects. They can be programmed to implement various functions, offering great flexibility and shorter time-to-market. However, they are generally less power-efficient and less performant than ASICs. They are good for prototyping, low-volume production, and applications requiring frequent design changes. Think of a prototype circuit board for a new algorithm.

In summary: ASICs are like a bespoke suit, perfectly tailored but expensive and time-consuming to create. FPGAs are like off-the-rack clothing – readily available and adaptable, but might not fit perfectly.

Q 18. Explain your experience with different verification methodologies (e.g., UVM).

My experience with verification methodologies encompasses various techniques, with a strong focus on UVM (Universal Verification Methodology). UVM provides a standardized and reusable framework for building complex verification environments. I’ve utilized UVM extensively for:

- Developing constrained-random verification: This allows for automated generation of test cases, covering a vast range of possible scenarios. This is far more efficient than manually creating test cases.

- Creating reusable verification components: UVM allows for building reusable components like drivers, monitors, and scoreboards, significantly reducing development time and improving testbench maintainability.

- Implementing functional coverage: UVM helps ensure that all aspects of the design are thoroughly tested by tracking and measuring functional coverage.

- Using assertions and formal verification techniques: These methods can help detect subtle design errors early in the development process.

In a recent project involving a high-speed data link, I used UVM to create a robust verification environment that included advanced techniques like coverage-driven verification and functional assertions. This allowed us to achieve high functional coverage and identify several critical bugs before tape-out. The use of UVM significantly reduced the overall verification time and improved the quality of the final product.

Q 19. How do you debug a failing digital circuit?

Debugging a failing digital circuit involves a systematic approach combining hardware and software techniques. The first step is to reproduce the failure consistently. Then, I typically follow these steps:

- Analyze simulation results: If simulations were performed, review the waveforms and logs to identify potential issues. This can pinpoint the exact location of the failure.

- Utilize logic analyzers and oscilloscopes: These tools provide real-time analysis of signals on the chip, allowing for observation of signal behavior during operation. This is critical for identifying timing issues or glitches.

- Employ boundary scan (JTAG): This allows for accessing internal nodes of the chip to inspect signals and perform tests.

- Use debug tools and in-circuit emulation: These advanced techniques permit debugging at various levels of abstraction.

- Code review and static analysis: This can be useful to identify potential coding errors.

For example, if a particular module within a processor stops responding, I might use a logic analyzer to examine the clock signals and control signals directed to that module. Observing a lack of a clock or incorrect control signals would clearly indicate the problem area. This systematic process, combining hardware debugging techniques with software-based analysis, significantly speeds up identification and solution of design faults.

Q 20. Explain your understanding of different types of latches and flip-flops.

Latches and flip-flops are fundamental building blocks of sequential digital circuits. They store binary data, but they differ in their behavior and triggering mechanisms.

- Latches: These are level-sensitive devices; their output follows the input as long as the enable signal is high. A simple example is an SR latch. They can be prone to metastability issues if the input changes while the enable signal is active.

- Flip-flops: These are edge-triggered devices; their output changes only on a specific edge (rising or falling) of the clock signal. Common types include D flip-flops, JK flip-flops, and T flip-flops. They are less susceptible to metastability than latches.

The choice between latches and flip-flops depends on the application. Flip-flops are generally preferred for synchronous designs due to their predictable behavior and immunity to metastability issues. Latches are sometimes used in asynchronous designs or for specific situations where level-sensitive behavior is desired, but caution is needed.

// Example Verilog code for a D flip-flop always @(posedge clk) begin if (enable) q <= d; end

Q 21. How do you optimize the power consumption of a digital circuit?

Optimizing the power consumption of a digital circuit is crucial for extending battery life in portable devices and reducing operating costs in larger systems. Several strategies can be employed:

- Clock gating: Disabling the clock signal to inactive parts of the circuit significantly reduces power consumption.

- Power gating: Completely powering down inactive blocks reduces leakage current and dynamic power.

- Low-power design techniques: Using low-threshold voltage transistors, reducing operating voltage, and optimizing the circuit topology are vital.

- Multi-voltage designs: Operating different parts of the circuit at different voltages can optimize overall power consumption.

- Design for sleep modes: Implementing low-power sleep modes to reduce power when the circuit is inactive. Proper power management circuitry is crucial here.

- Careful use of registers and memory: Minimizing data movement and using smaller memory structures can reduce power.

For instance, in a complex system-on-chip (SoC), we might use clock gating to disable parts of the processor or memory controller when not in active use. This significantly reduces power consumption without impacting functionality when those modules are not needed. Power optimization is not just about individual gates but a holistic approach involving architecture, design, and implementation.

Q 22. Explain your experience with different design flows.

My experience encompasses various IC design flows, from front-end to back-end. I'm proficient in both ASIC (Application-Specific Integrated Circuit) and FPGA (Field-Programmable Gate Array) design methodologies. In the front-end, I've worked extensively with RTL (Register-Transfer Level) design using languages like Verilog and VHDL, performing tasks like design partitioning, coding, and simulation. I've used high-level synthesis (HLS) tools for accelerating design exploration and for targeting FPGAs. The back-end involves synthesis, optimization, place and route, and physical verification. I've utilized industry-standard tools like Synopsys Design Compiler, Cadence Innovus, and Mentor Graphics Olympus-SoC. For example, on a recent project involving a high-speed data converter, I used HLS to generate optimized RTL from a C++ model, significantly reducing development time and improving performance compared to a purely manual RTL approach. In another project, a complex network-on-chip (NoC) design, I employed a hierarchical design methodology to manage the design complexity effectively, breaking down the design into manageable blocks, and employing hierarchical verification. This allowed us to quickly identify and resolve issues in the NoC architecture.

Q 23. Describe your experience with formal verification tools.

Formal verification is crucial for ensuring design correctness. My experience includes using tools like Cadence Conformal and Jasper formal verification tools. I've used these tools to prove the absence of certain design errors, such as deadlocks, assertion violations, and equivalence checks between different design versions. For instance, in a recent project, I used Conformal to formally verify the data path of a complex processor core, ensuring data integrity and preventing potential race conditions. Formal verification is particularly effective in finding subtle bugs that are hard to detect with simulations alone. I typically use a combination of formal and simulation-based verification to create a robust verification plan. The key is to strategically apply formal verification to the most critical and complex parts of the design, maximizing its effectiveness and minimizing run time.

Q 24. Explain the importance of floorplanning and placement in IC design.

Floorplanning and placement are critical steps in the physical design flow. Floorplanning involves the initial arrangement of major blocks within the chip, focusing on optimizing area, power consumption, and signal routing. Placement precisely positions individual cells, considering factors such as timing constraints and signal interconnections. Good floorplanning minimizes wire length, reduces congestion, and improves overall performance. Poor floorplanning can lead to timing closure issues and increased power consumption. Imagine it like designing a city: floorplanning is akin to deciding the location of major landmarks (like airports and hospitals), while placement is deciding where each building goes. Both steps are crucial for creating an efficient and functional city (chip). For example, in a high-performance processor design, I strategically placed critical blocks near each other to minimize clock delays and improve timing performance. I also used advanced placement techniques to reduce congestion in critical areas of the chip.

Q 25. How do you handle timing closure in your designs?

Timing closure is a crucial aspect of IC design, ensuring that all paths meet the specified timing constraints. My approach involves a combination of design optimization, constraint management, and timing analysis. This begins early in the design process; constraining the design appropriately in the early stages is vital. I utilize static timing analysis (STA) tools to identify timing violations and iteratively refine the design through optimizations such as clock tree synthesis (CTS), buffer insertion, and other physical design techniques. For example, during a high-speed memory controller design, I had to work closely with the place and route team to adjust the placement to minimize routing delays. We employed multiple iterations of STA and optimization to achieve timing closure while meeting power constraints. Understanding the trade-offs between area, power, and performance is crucial in this process. Sometimes, it requires re-examining the RTL design or adjusting the constraints to achieve a feasible solution.

Q 26. Describe your experience with different routing tools.

My experience with routing tools includes Cadence Innovus and Mentor Graphics Olympus-SoC. These tools automate the process of connecting different components on a chip. Effective routing is crucial for achieving timing closure and minimizing power consumption. Different algorithms are employed for different applications. For instance, in high-speed designs, I've used tools that optimize for low skew and minimal delay. In other applications where area is paramount, I've prioritized minimizing wire length. Advanced routing techniques such as global routing, detailed routing, and congestion mitigation are essential for complex designs. For example, in a recent project involving a large SoC, I used congestion-aware routing techniques to effectively manage routing resources and successfully complete the routing process without significant timing violations.

Q 27. What are your experiences with different physical verification tools?

Physical verification tools are essential for ensuring the physical integrity of the design. I have experience with tools like Calibre and Assura. These tools perform checks such as Design Rule Checking (DRC), Layout Versus Schematic (LVS), and Extraction to ensure that the layout meets the specified design rules and matches the schematic. DRC verifies that the layout adheres to manufacturing process rules to prevent fabrication issues. LVS checks that the layout correctly implements the electrical functionality as intended. Extraction generates a netlist from the layout for further analysis. For example, during a recent project, I used Calibre DRC to identify and fix layout violations that could have resulted in manufacturing defects. Thorough physical verification is crucial to avoid costly redesigns and ensure high chip yield.

Q 28. Explain your understanding of electromigration and how to mitigate it.

Electromigration is the gradual movement of metal ions in a conductor due to high current density. This can lead to open circuits or shorts, causing chip failure. Mitigating electromigration involves careful design choices. One crucial strategy is reducing current density by using wider metal lines, multiple metal layers, and optimizing the routing to distribute current more evenly. Another approach is to select materials with high electromigration resistance. During the design process, I employ simulations and analysis tools to assess electromigration risks. For instance, I might use a tool like Ansys RedHawk to analyze current density in the design and identify potential hot spots. Based on the analysis, I make necessary design modifications, such as increasing metal width or rerouting signals, to reduce the current density and mitigate electromigration risk. This proactive approach is vital for ensuring the long-term reliability of the chip.

Key Topics to Learn for IC Design Interview

- Digital Design Fundamentals: Mastering logic gates, Boolean algebra, combinational and sequential logic circuits is crucial. Understand the design process from concept to implementation.

- VLSI Design Flow: Familiarize yourself with the entire IC design flow, from HDL coding (Verilog/VHDL) to synthesis, place and route, and physical verification. Be prepared to discuss trade-offs at each stage.

- Timing Analysis and Optimization: Understand concepts like setup and hold time, critical path analysis, and clock tree synthesis. Knowing how to optimize for timing is key.

- Low-Power Design Techniques: Explore various techniques to minimize power consumption in ICs, including clock gating, power gating, and voltage scaling. Discuss their trade-offs.

- Memory Systems: Gain a solid understanding of various memory architectures (SRAM, DRAM, Flash), their characteristics, and applications. Be prepared to discuss memory controllers and interfaces.

- Verilog/VHDL Coding and Simulation: Develop strong coding skills in at least one HDL and be comfortable simulating and debugging your designs. Understand testbenches and verification methodologies.

- Physical Design and Layout: Understand the basics of physical design, including floorplanning, placement, routing, and physical verification. Discuss challenges and optimization techniques.

- Static Timing Analysis (STA): Demonstrate a thorough understanding of STA, including constraint definition, timing report interpretation, and timing closure techniques.

- Problem-Solving and Design Methodology: Practice breaking down complex problems into smaller, manageable tasks. Showcase your ability to think critically and creatively while designing circuits.

Next Steps

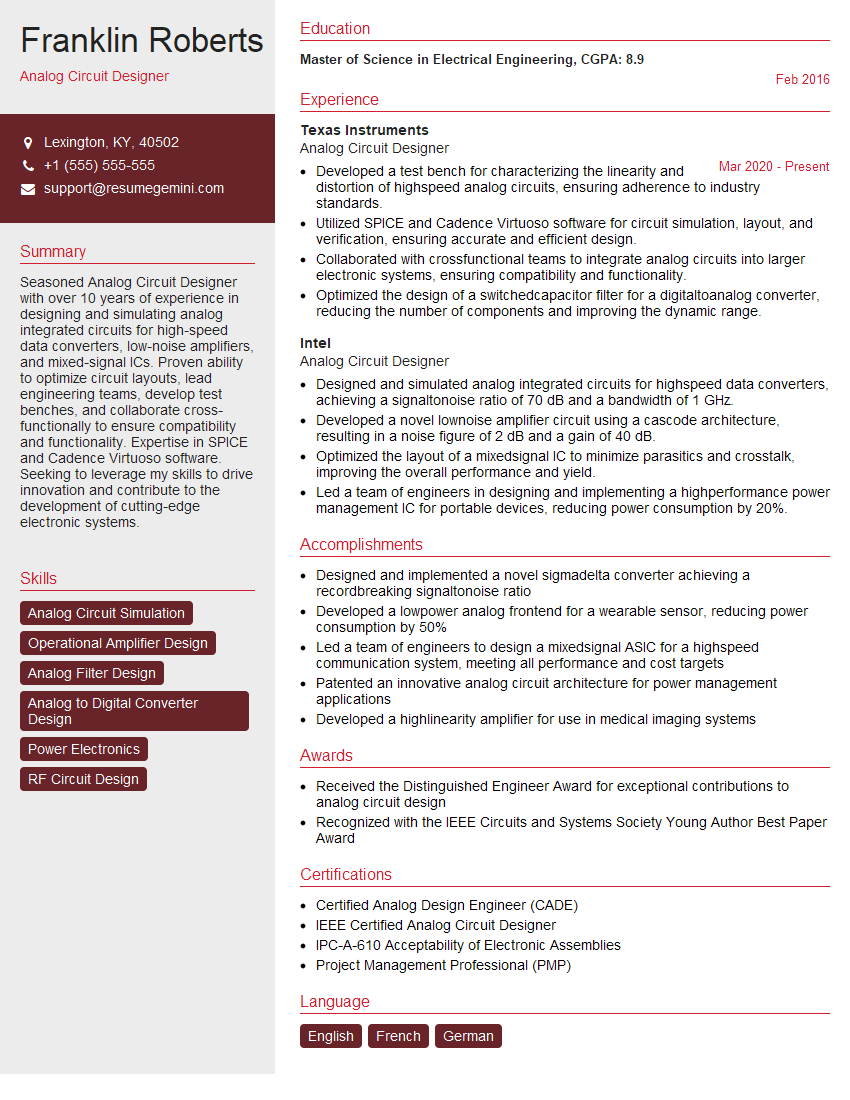

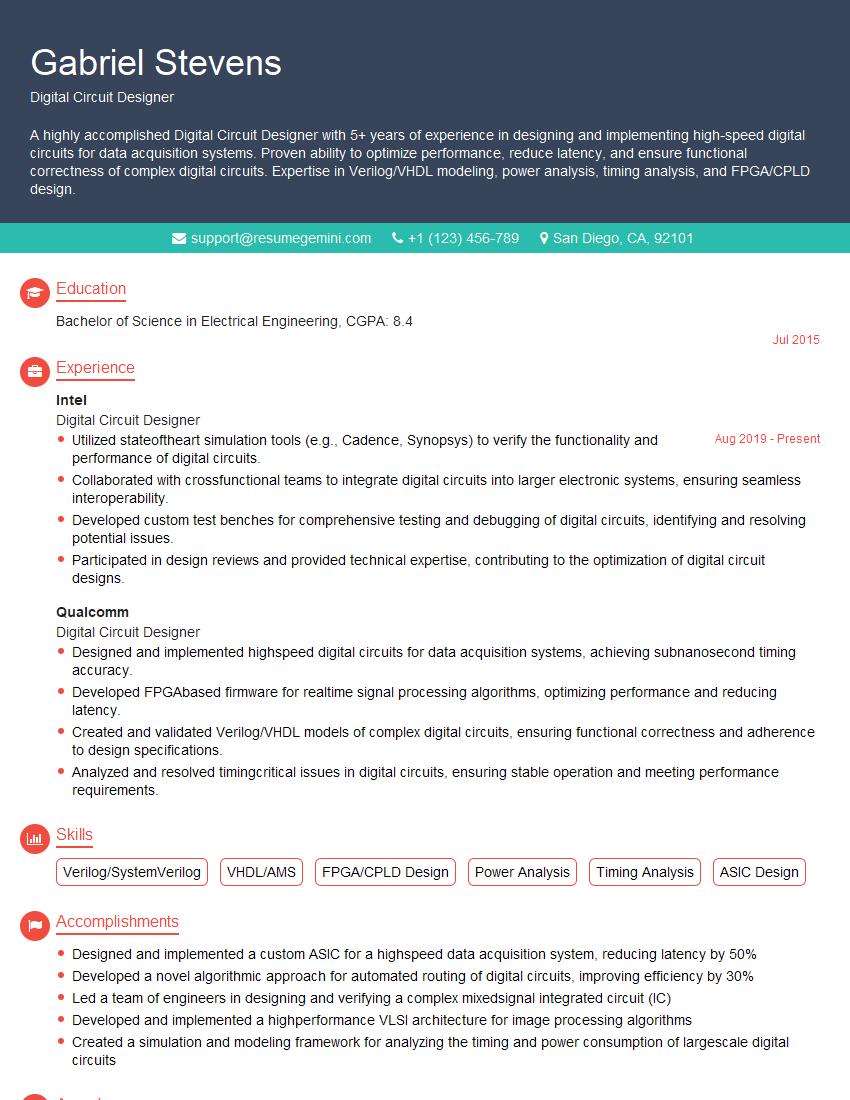

Mastering IC design opens doors to a rewarding career with significant growth potential in a constantly evolving field. To maximize your job prospects, it's vital to present your skills effectively. Creating an ATS-friendly resume is crucial for getting your application noticed. We recommend using ResumeGemini, a trusted resource, to build a professional and impactful resume that highlights your accomplishments and technical expertise. Examples of resumes tailored to IC Design are available to help guide you.

Explore more articles

Users Rating of Our Blogs

Share Your Experience

We value your feedback! Please rate our content and share your thoughts (optional).

What Readers Say About Our Blog

Very informative content, great job.

good