Every successful interview starts with knowing what to expect. In this blog, we’ll take you through the top Processor operation interview questions, breaking them down with expert tips to help you deliver impactful answers. Step into your next interview fully prepared and ready to succeed.

Questions Asked in Processor operation Interview

Q 1. Explain the difference between RISC and CISC architectures.

RISC (Reduced Instruction Set Computer) and CISC (Complex Instruction Set Computer) architectures represent two fundamental approaches to processor design. The core difference lies in the complexity and number of instructions each supports.

CISC processors utilize a large number of complex instructions, each capable of performing multiple operations. Think of a Swiss Army knife – one tool can perform many tasks. This complexity often requires more transistors and a more intricate design, leading to potentially slower clock speeds but potentially fewer instructions needed to complete a task. Examples include the early x86 architectures.

RISC processors, in contrast, favor a smaller set of simpler instructions, each executing in a single clock cycle. This streamlined approach allows for faster clock speeds and simpler design, making them more energy-efficient. It’s like having a set of specialized tools – each does one job exceptionally well. Examples include ARM architectures commonly found in smartphones and embedded systems.

In practice, the lines have blurred somewhat. Modern CISC processors often employ RISC-like techniques internally, translating complex instructions into simpler micro-operations before execution. Similarly, some RISC designs have incorporated more complex instructions.

Q 2. Describe the stages of a typical processor pipeline.

A typical processor pipeline breaks down instruction execution into a series of stages, allowing multiple instructions to be processed concurrently. Imagine an assembly line in a factory; each stage performs a specific task, increasing overall throughput.

- Instruction Fetch (IF): Retrieves the next instruction from memory.

- Instruction Decode (ID): Decodes the fetched instruction to determine the operation and operands.

- Execute (EX): Performs the arithmetic or logical operation specified by the instruction.

- Memory Access (MEM): Accesses memory to read or write data if required by the instruction.

- Write Back (WB): Writes the result of the operation back to the register file.

Each stage operates on a different instruction simultaneously. This parallel processing significantly boosts performance compared to sequential execution. However, hazards like data dependencies and branch prediction can impact pipeline efficiency. Sophisticated techniques are employed to mitigate these issues, such as forwarding and branch prediction.

Q 3. What are the various types of processor caches and their functions?

Processor caches are small, fast memory units situated between the processor and main memory. They store frequently accessed data, reducing the time it takes to retrieve information. Think of it as a chef keeping frequently used ingredients close at hand.

- L1 Cache: The smallest and fastest cache, typically integrated directly onto the processor die. It’s further divided into L1 data cache and L1 instruction cache.

- L2 Cache: Larger and slower than L1, but still significantly faster than main memory. It’s often shared by all processor cores.

- L3 Cache: The largest and slowest level of cache, often shared across multiple cores or even multiple processors. It acts as a buffer between the L2 cache and main memory.

The function of each cache level is to minimize memory access latency. Data is moved between cache levels based on various replacement policies (like LRU – Least Recently Used) to optimize performance. The higher the cache level, the larger its capacity but slower its access speed.

Q 4. Explain the concept of cache coherence.

Cache coherence refers to the consistency of data stored in multiple caches within a multiprocessor system. It ensures that all processors see the same up-to-date values for shared data. Imagine multiple chefs working with the same ingredients – they need to ensure everyone is using the freshest versions to avoid inconsistencies.

Without cache coherence, different processors might have different copies of the same data, leading to data corruption and unpredictable results. Several protocols, like MESI (Modified, Exclusive, Shared, Invalid) are used to maintain coherence. These protocols use hardware mechanisms to track changes in shared data and propagate updates across caches.

Q 5. How does virtual memory work?

Virtual memory is a memory management technique that provides each process with its own seemingly continuous address space, even if the physical memory available is limited. It creates the illusion of having more memory than is physically present.

Virtual addresses generated by a program are translated to physical addresses using a page table. This table maps virtual pages to physical frames in RAM. Pages not currently in use are stored on the hard drive (swap space). When a process accesses a page not in RAM, a page fault occurs, triggering the operating system to load the page from the hard drive into RAM.

This technique allows multiple programs to run concurrently, each believing it has exclusive access to its address space. It also improves memory utilization by only loading active pages into RAM, leaving inactive pages on the hard drive.

Q 6. Describe different memory addressing modes.

Memory addressing modes specify how the effective address of an operand is calculated. Different modes provide flexibility in accessing data from memory.

- Immediate Addressing: The operand value is included directly in the instruction itself.

- Register Addressing: The operand is located in a CPU register.

- Direct Addressing: The operand address is specified directly in the instruction.

- Indirect Addressing: The instruction specifies a memory location that contains the address of the operand.

- Register Indirect Addressing: The address of the operand is stored in a register.

- Displacement Addressing: The effective address is calculated by adding a displacement value to the contents of a register or a base address.

The choice of addressing mode affects instruction length, execution speed, and programming convenience. For example, immediate addressing is efficient for small constants but less flexible for larger values.

Q 7. Explain the function of a memory management unit (MMU).

The Memory Management Unit (MMU) is a hardware component that manages the translation of virtual addresses to physical addresses in a virtual memory system. It acts as a crucial intermediary between the CPU and RAM, enabling efficient memory management and protection.

The MMU uses page tables to perform this translation. It intercepts memory access requests from the CPU, determines the corresponding physical address, and then forwards the request to the memory controller. The MMU also plays a vital role in memory protection by ensuring that a process can only access its allocated memory space, preventing unauthorized access and crashes.

In essence, the MMU ensures that multiple processes can run concurrently without interfering with each other’s memory, utilizing virtual memory effectively while maintaining system stability.

Q 8. What are interrupts and how are they handled by a processor?

Interrupts are signals that temporarily suspend the normal execution of a processor’s program to handle a more urgent event. Think of it like a phone call interrupting your work – you pause what you’re doing to answer the call, then resume afterward. These events can originate from various sources, such as hardware devices (like a keyboard press or a disk read completion) or software (like an error condition).

The processor handles interrupts through a predefined sequence:

- Interrupt Request (IRQ): A device or software generates an interrupt request.

- Interrupt Recognition: The processor detects the IRQ.

- Interrupt Handling: The processor saves the current state of its execution (registers, program counter, etc.) onto a stack. This ensures a smooth return to the original program later.

- Interrupt Vector Table Lookup: The processor uses the interrupt number (identifying the source of the interrupt) to locate the address of the corresponding interrupt handler routine (a specialized piece of code designed to handle that specific interrupt) in a table called the Interrupt Vector Table (IVT).

- Interrupt Service Routine (ISR) Execution: The processor executes the ISR, which handles the event that triggered the interrupt (e.g., reading data from the keyboard, handling a disk error).

- Return from Interrupt (IRET): Once the ISR is complete, the processor restores the saved state from the stack and resumes execution from where it left off before the interrupt.

For example, when you press a key on your keyboard, the keyboard controller sends an interrupt to the processor. The processor handles this interrupt, reads the key pressed, and updates the input buffer. This is done without noticeably interrupting your workflow.

Q 9. Explain the concept of DMA (Direct Memory Access).

Direct Memory Access (DMA) is a technique that allows certain hardware subsystems to access system memory (RAM) independently of the CPU. Imagine a busy waiter (CPU) constantly carrying food (data) from the kitchen (peripheral device) to the tables (RAM). DMA is like having a separate conveyor belt that directly transports food from the kitchen to the tables, freeing the waiter to focus on other tasks. This significantly speeds up data transfer, especially for large amounts of data.

The DMA controller manages this process. It takes control of the memory bus, directly transferring data between the peripheral device and memory without involving the CPU’s intervention. The CPU only needs to initiate the transfer and can then proceed with other operations while the DMA controller handles the data transfer. This significantly improves performance, reducing the CPU’s workload and minimizing processing delays.

A practical application is transferring a large file from a hard drive to RAM. Without DMA, the CPU would have to handle every byte, resulting in slow speeds. With DMA, the hard drive directly transfers the data to RAM, allowing the CPU to perform other tasks concurrently, thus making the process much faster.

Q 10. How does a processor handle exceptions?

Exceptions are similar to interrupts but are typically triggered by software events rather than hardware. They indicate an unexpected or exceptional condition during program execution that requires immediate attention. Think of it like encountering a roadblock while driving – you need to handle it to continue your journey.

The processor handles exceptions via a similar mechanism as interrupts:

- Exception Recognition: The processor detects the exceptional condition (e.g., division by zero, illegal instruction, memory access violation).

- Exception Handling: The processor saves the current program state onto the stack.

- Exception Vector Table Lookup: The processor looks up the appropriate exception handler based on the type of exception in the Exception Vector Table (EVT), which is analogous to the IVT for interrupts.

- Exception Handler Execution: The processor executes the exception handler, which attempts to resolve the exceptional condition or to terminate the program gracefully.

- Return from Exception: If the exception can be handled, the processor restores the saved state and resumes execution; otherwise, the program terminates.

For example, attempting to divide by zero will trigger an exception, preventing the program from crashing unexpectedly. The exception handler can display an error message or take other corrective actions.

Q 11. Describe different types of processor buses.

Processor buses are sets of electrical conductors that transfer data between different components of the computer system. They are crucial for communication within the computer. They are usually categorized into three main types:

- Address Bus: Used to specify the memory location or I/O device the processor wants to access. It’s a unidirectional bus, meaning data flows only in one direction (from the CPU to memory/I/O).

- Data Bus: Used to transfer data between the CPU, memory, and I/O devices. It’s a bidirectional bus, capable of transferring data in both directions.

- Control Bus: This set of lines carries control signals that coordinate the activities of all components. It includes signals like read/write, memory request, interrupt signals, etc. The direction of data flow varies depending on the specific signal.

Modern processors might also utilize more specialized buses, such as the Front Side Bus (FSB) which connected the CPU to the north bridge chipset (in older systems) or newer interconnect technologies like PCIe and UPI (Ultra Path Interconnect) for high-speed communication between various components within the system. The choice of bus architecture significantly impacts the overall system performance and speed.

Q 12. Explain the role of a clock in a processor.

The clock in a processor is a crystal oscillator that generates a regular series of electrical pulses. These pulses act like a metronome, synchronizing the operations within the processor, ensuring that all components work in a coordinated manner. Each pulse represents a clock cycle, the basic unit of time for the processor’s operations.

The clock speed, measured in Hertz (Hz) or gigahertz (GHz), represents the number of clock cycles per second. A higher clock speed generally means the processor can execute more instructions per second. However, clock speed isn’t the only factor determining processor performance; other factors such as the processor’s architecture and instruction set also play significant roles. The clock signal synchronizes the fetching, decoding, and execution of instructions. Without a clock, the processor wouldn’t know when to perform each step, resulting in chaotic and unpredictable behavior.

Q 13. What are the various power management techniques in processors?

Power management is critical in modern processors, especially in mobile devices, to extend battery life and reduce heat generation. Several techniques are employed:

- Clock Gating: Disabling the clock signal to parts of the processor that are not currently in use, thus reducing power consumption. This is like turning off lights in unused rooms.

- Voltage Scaling: Reducing the operating voltage of the processor when it’s under light load. Lower voltage reduces power dissipation (P=IV, power is voltage times current). It’s analogous to using a dimmer switch for a light.

- Power States: Processors can operate in various power states (e.g., sleep, idle, active) each with different power consumption levels. This allows the processor to dynamically adjust its power consumption based on the workload.

- Thermal Throttling: If the processor gets too hot, it automatically reduces its clock speed to prevent damage. This is like a car’s overheating protection system.

- Dynamic Frequency Scaling: The processor adjusts its clock speed dynamically based on the current demand, increasing the clock speed for heavy tasks and decreasing it for lighter tasks. This is akin to an automatic transmission that adjusts gear ratios depending on speed and load.

These techniques work in tandem to optimize power consumption while maintaining acceptable performance levels. The specific techniques used vary depending on the processor architecture and application.

Q 14. What are the common performance metrics for processors?

Several metrics measure processor performance, and the most suitable one depends on the specific application. Some common ones include:

- Clock Speed (GHz): Indicates the number of clock cycles per second. Higher clock speed often implies faster processing but not always.

- Instructions Per Second (IPS): Measures the number of instructions the processor can execute per second.

- Millions of Instructions Per Second (MIPS): Similar to IPS but expressed in millions.

- Floating-Point Operations Per Second (FLOPS): Specifically measures the processor’s ability to perform floating-point arithmetic, essential for scientific and graphics applications.

- CPI (Cycles Per Instruction): A measure of efficiency, representing the average number of clock cycles required to execute a single instruction. A lower CPI signifies higher efficiency.

- Benchmark Scores: Synthetic benchmarks (like SPECint, SPECfp) and real-world application benchmarks (e.g., measuring video encoding time) provide a comprehensive performance evaluation.

- Cache Size and Performance: Larger and faster caches (L1, L2, L3) significantly impact performance by reducing memory access times.

It’s important to consider multiple metrics when evaluating a processor’s performance, rather than solely focusing on clock speed. Real-world benchmarks offer the most realistic assessment of processor capabilities in specific use cases.

Q 15. Explain Amdahl’s Law and its relevance to processor performance.

Amdahl’s Law describes the theoretical speedup in latency of a program’s execution when only a part of that program is improved. Imagine you’re baking a cake; even if you double the speed of the oven (improving one part of the process), the overall baking time won’t double because you’re still limited by other steps like mixing and frosting. Formally, it’s expressed as: Speedup = 1 / [(1 – P) + (P / S)], where P is the fraction of work that can be parallelized or improved, and S is the speedup of the improved part.

In processor performance, Amdahl’s Law highlights that even with massive improvements in a specific area (like clock speed or instruction count), overall performance gains are capped by the parts that can’t be improved. For instance, if 10% of a program is inherently sequential, even if the remaining 90% is sped up infinitely, the maximum overall speedup is only 10x (1 / (0.1 + 0.9/∞) = 1/0.1 = 10).

This law is crucial for processor architects as it guides resource allocation. Spending vast resources improving parts with negligible impact on overall performance yields diminishing returns. Instead, focusing on optimizing the performance bottlenecks yields better results.

Career Expert Tips:

- Ace those interviews! Prepare effectively by reviewing the Top 50 Most Common Interview Questions on ResumeGemini.

- Navigate your job search with confidence! Explore a wide range of Career Tips on ResumeGemini. Learn about common challenges and recommendations to overcome them.

- Craft the perfect resume! Master the Art of Resume Writing with ResumeGemini’s guide. Showcase your unique qualifications and achievements effectively.

- Don’t miss out on holiday savings! Build your dream resume with ResumeGemini’s ATS optimized templates.

Q 16. How does pipelining improve processor performance?

Pipelining in processors is like an assembly line. Instead of completing one instruction entirely before starting the next, different stages of instruction processing occur concurrently. Think of it as having multiple workers each performing a specific step on a series of instructions, rather than one worker completing each instruction individually.

Consider a simplified instruction processing with five stages: Fetch, Decode, Execute, Memory, Writeback. Without pipelining, each instruction takes five clock cycles. With pipelining, after the first instruction completes the Fetch stage, a second instruction begins its Fetch stage, and so on. This overlapping allows for multiple instructions to be in progress simultaneously.

The benefit is a significant increase in Instructions Per Cycle (IPC). While the first instruction still takes five cycles, subsequent instructions complete every single cycle, after the initial pipeline fill. This leads to a substantial performance boost. However, hazards like data dependencies and branch mispredictions can cause pipeline stalls, reducing the effective throughput.

Q 17. Explain the concept of branch prediction.

Branch prediction is a crucial technique used to improve the performance of pipelined processors. Programs often contain conditional statements (if-then-else) or loops that alter the flow of instruction execution. These branches create uncertainty about the next instruction to fetch and execute. Without prediction, the processor must wait until the branch condition is resolved before proceeding, leading to pipeline stalls.

Branch prediction attempts to guess which branch will be taken before the condition is evaluated. This guess is made using various algorithms, such as static prediction (always predicting the same branch) or dynamic prediction (using a history table to track past branch outcomes). If the prediction is correct, instruction fetching continues seamlessly; if incorrect, the pipeline must be flushed and restarted with the correct instructions. An incorrect prediction leads to performance penalties.

Modern processors use sophisticated algorithms, including branch target buffers and predictor tables, to improve the accuracy of branch prediction. Accurate prediction is key to maintaining high IPC, and advancements in this area significantly impact processor performance.

Q 18. What are superscalar processors?

Superscalar processors can execute multiple instructions simultaneously. Unlike pipelining, which processes instructions in a sequential order but in parallel stages, a superscalar processor can issue and execute multiple instructions in one clock cycle, provided there are no dependencies between them. Imagine having multiple assembly lines working concurrently instead of just one.

This capability requires sophisticated hardware, including multiple execution units, instruction decoders, and sophisticated scheduling logic to identify independent instructions that can be executed in parallel. The compiler also plays a critical role by generating code that facilitates parallel execution.

Superscalar processors boost performance significantly by achieving high IPC, but their effectiveness is limited by instruction-level parallelism (ILP) in the program, the availability of independent instructions, and the hardware’s ability to identify and execute them concurrently.

Q 19. Describe different types of instruction-level parallelism.

Instruction-level parallelism (ILP) refers to the ability to execute multiple instructions simultaneously. Several techniques exploit ILP:

- Multiple Issue: Issuing multiple instructions in a single clock cycle.

- Pipelining: Overlapping the execution stages of multiple instructions.

- Superscalar Execution: Combining multiple issue and pipelining to execute multiple instructions concurrently using multiple execution units.

- VLIW (Very Long Instruction Word): Packing multiple independent instructions into a single, very long instruction word. This requires the compiler to perform significant scheduling and optimization to ensure the instructions are indeed independent.

- Out-of-Order Execution: Executing instructions in an order different from the program order to maximize the utilization of execution units and hide pipeline stalls (discussed in detail below).

The amount of ILP available in a program is highly dependent on the program itself and how the compiler optimizes it. Programs with plenty of independent instructions benefit more from these techniques.

Q 20. Explain the concept of out-of-order execution.

Out-of-order execution is a sophisticated technique used in modern processors to enhance performance. It allows instructions to be executed in an order different from their program order, provided there are no data dependencies that would violate program semantics. Think of it like a chef preparing multiple dishes simultaneously, rather than preparing each one completely before starting the next. Some steps might finish early, so the chef moves on to others without waiting for all steps of the previous dish to be finished.

This technique helps overcome pipeline stalls caused by various hazards, such as data dependencies (one instruction needing the result of a previous instruction) and branch mispredictions. By executing instructions that are ready, out-of-order execution keeps the processor busy and improves performance. It requires complex hardware mechanisms such as a reservation station, reorder buffer, and sophisticated scheduling algorithms. However, implementing out-of-order execution significantly increases hardware complexity and power consumption.

Q 21. What are the trade-offs between performance and power consumption in processor design?

There’s an inherent trade-off between performance and power consumption in processor design. Increasing performance often comes at the cost of higher power consumption, and vice-versa. For example, increasing clock speed improves performance, but also exponentially increases power dissipation (Power ∝ frequency²).

Several design choices reflect this trade-off:

- Higher clock speeds vs. lower power modes: Higher clock speeds lead to faster processing but consume more power. Lower power modes are slower but are essential for battery-powered devices.

- Larger caches vs. smaller caches: Larger caches improve performance by reducing memory access latency, but require more transistors and consume more power.

- More complex instruction sets vs. simpler RISC architectures: Complex instructions offer potential for higher performance but often require more transistors and more power per instruction.

- Out-of-order execution vs. in-order execution: Out-of-order execution significantly boosts performance but requires complex hardware and consumes more power.

Processor designers constantly seek optimal balance points depending on the target application and market requirements. High-performance computing (HPC) processors emphasize raw performance, even at the cost of high power consumption, while mobile processors prioritize low power consumption while maintaining acceptable performance.

Q 22. Describe different types of processor packaging.

Processor packaging refers to the physical structure that houses the processor die and provides interfaces for connecting to other components on a motherboard. Different packaging options offer various trade-offs in terms of cost, performance, and power consumption.

- Land Grid Array (LGA): In LGA packaging, the processor die has tiny metal contacts called pins, which sit on a socket with corresponding holes. This approach is common in desktop CPUs. The advantage is that the pins are on the motherboard, reducing the risk of bending delicate pins on the processor itself. Intel’s CPUs often use this type of packaging.

- Pin Grid Array (PGA): In PGA packaging, the processor die itself has pins that insert into a socket on the motherboard. This type is less common now due to the greater risk of bending the pins on the CPU. Older AMD CPUs frequently employed this packaging.

- Ball Grid Array (BGA): BGA packaging uses solder balls to connect the processor die to the motherboard. It’s commonly used in embedded systems and laptops where smaller form factors are required. The soldering process makes it less user-friendly for replacing CPUs.

- Organic Chip Carrier (OCC): This is an older packaging style with pins arranged along the edges of a plastic package. It was often found in early microprocessors.

- Ceramic Dual In-line Package (CDIP): An older packaging method that also offered a form factor more conducive to larger chips compared to DIP.

The choice of packaging depends heavily on factors like the processor’s power requirements, intended applications, and cost constraints. For instance, a high-end desktop processor might utilize a robust LGA package for easy installation and upgradeability, whereas a low-power embedded system might prefer a space-saving BGA package.

Q 23. Explain the concept of thermal design power (TDP).

Thermal Design Power (TDP) is a metric that represents the maximum amount of heat a processor is expected to generate under typical operating conditions. It’s measured in watts (W). Think of TDP as the processor’s ‘recommended’ power consumption when under a typical workload, like general web browsing or office productivity. It’s crucial for selecting appropriate cooling solutions (like heatsinks or liquid coolers) to prevent overheating, which can lead to performance throttling or even damage.

Manufacturers determine TDP values through rigorous testing, considering various aspects like clock speeds, voltage levels, and typical workloads. For example, a processor with a TDP of 65W is likely to generate around 65W of heat under typical loads, whereas a processor with a TDP of 125W might generate significantly more heat if pushed to its limits. However, note that TDP doesn’t represent the *absolute* maximum power draw; a processor can draw more power under extreme workloads (like gaming or intensive computations), exceeding its rated TDP.

Understanding TDP is vital for system builders as it helps them choose compatible cooling solutions and prevent system instability or hardware failure due to excessive heat. Overclocking a processor further increases its TDP; therefore it is critical to take this into account when selecting appropriate cooling solutions.

Q 24. How does a processor handle floating-point arithmetic?

Processors handle floating-point arithmetic using specialized hardware units called Floating-Point Units (FPUs). FPUs are designed to efficiently perform calculations on numbers represented in floating-point format, which allows for representing a wider range of values (including very large and very small numbers) compared to integer representation. The FPU operates independently from the main arithmetic logic unit (ALU), which handles integer arithmetic.

The FPU typically implements instructions according to the IEEE 754 standard, which dictates how floating-point numbers are represented and how operations are performed. These instructions allow for various operations such as addition, subtraction, multiplication, division, square roots, and trigonometric functions. The process involves several steps, including:

- Data fetching: The FPU retrieves the floating-point operands from registers or memory.

- Exponent adjustment: The exponents of the operands are aligned to ensure proper addition or subtraction.

- Mantissa operation: The mantissas (the fractional parts) are added, subtracted, multiplied, or divided according to the operation.

- Normalization: The result is normalized to meet the IEEE 754 standard.

- Rounding: The result might be rounded to fit the desired precision.

- Storing the result: The computed result is then stored back into registers or memory.

Modern processors often have multiple FPUs or even vectorized FPUs (like SIMD units) to speed up floating-point computations. This parallel processing dramatically reduces the execution time of floating-point operations frequently found in scientific computing, graphics processing, and simulations.

Q 25. What are the different types of processor cores?

Processor cores are the fundamental processing units within a processor. Different types exist, each with its own characteristics and trade-offs:

- Single-core processors: These processors have only one core, meaning they can execute one instruction at a time. They are less powerful but simpler and more energy-efficient.

- Multi-core processors: These processors have multiple cores, allowing for parallel processing. Each core can execute instructions concurrently, significantly improving performance for multi-threaded applications. This is the dominant architecture in modern processors. Examples include dual-core, quad-core, hexa-core, octa-core, and even processors with dozens of cores.

- Big.LITTLE cores: This heterogeneous architecture employs a mix of high-performance cores (the ‘big’ cores) for demanding tasks and energy-efficient cores (the ‘little’ cores) for low-power operations. This configuration strikes a balance between performance and power consumption, often seen in mobile devices.

- Hyper-threading (or SMT): This technology allows a single physical core to appear as multiple logical cores to the operating system. It improves performance by allowing the core to switch between different threads quickly. However, this doesn’t double performance; the benefits are application-dependent.

The type of core architecture used is a critical aspect in determining a processor’s performance, power consumption, and suitability for various tasks. High-performance computing applications usually benefit from processors with many high-performance cores, while mobile devices might prefer a Big.LITTLE configuration to extend battery life.

Q 26. Explain the role of a microcode in processor operation.

Microcode is a low-level firmware program embedded within a processor’s control unit. It acts as an interpreter, translating higher-level machine instructions into a series of micro-operations that the processor’s hardware can execute directly. Think of it as a layer of software that sits between the machine instructions and the hardware. This abstraction allows for flexibility and facilitates the implementation of complex instructions without requiring extensive hardware modifications.

The microcode handles tasks like:

- Instruction decoding: Interpreting the machine instruction and determining the necessary steps to execute it.

- Micro-operation sequencing: Controlling the order in which the micro-operations are executed.

- Register access: Managing access to the processor’s internal registers.

- Data handling: Performing the necessary data transfers and manipulations.

- Exception handling: Managing errors and exceptions during instruction execution.

Microcode updates can be used to fix bugs, enhance performance, or add new instructions without needing to replace the entire processor. However, changes to microcode can impact processor functionality, and incorrectly implemented microcode can have severe consequences. The microcode is typically stored in a read-only memory (ROM) or flash memory within the processor.

Q 27. Describe the different stages of processor design flow.

The processor design flow is a complex process involving multiple stages:

- Specification: Defining the processor’s architecture, instruction set, and performance targets.

- Microarchitecture design: Designing the internal structure of the processor, including the pipeline, caches, and other components.

- RTL design: Writing Register-Transfer Level (RTL) code, which describes the processor’s functionality using a hardware description language like Verilog or VHDL.

- Logic synthesis: Transforming the RTL code into a netlist, a representation of the processor’s logic gates and interconnections.

- Physical design: Placing and routing the logic gates and other components on the silicon die, optimizing for area, power, and performance.

- Verification: Rigorously testing the design at various stages using simulation, formal verification, and emulation to ensure correctness and functionality. This is a critical step to minimize errors before fabrication.

- Fabrication: Manufacturing the processor on silicon wafers.

- Testing: Testing the manufactured processors to ensure they meet specifications.

- Packaging: Packaging the die into a suitable form factor.

Each of these stages is crucial for creating a functional and efficient processor. Any flaw in the design or fabrication process could lead to a defective chip.

Q 28. Explain the use of simulation and verification in processor design.

Simulation and verification are essential steps in processor design, ensuring the design works as intended before it’s physically fabricated. This is crucial because fabrication is expensive and time-consuming, and errors discovered after fabrication can be extremely costly to fix.

Simulation: Uses software tools to model the processor’s behavior and test its functionality under various conditions. Different levels of simulation exist:

- Functional simulation: Tests the processor’s behavior at a high level of abstraction, focusing on the correctness of the algorithms and instruction set architecture.

- Cycle-accurate simulation: Simulates the processor’s behavior at the clock-cycle level, providing more accurate timing information.

Verification: Goes beyond simple simulation and employs various techniques to rigorously check the design’s correctness. Techniques include:

- Formal verification: Mathematically proves the correctness of the design using formal methods.

- Emulation: Using a hardware emulator to execute the processor’s design at close-to-real-time speed, allowing for more realistic testing.

- Random testing: Running many random tests to uncover subtle bugs that might be missed by more structured approaches.

- Code coverage analysis: Measures the percentage of the design that has been tested to identify potential gaps in testing.

By combining simulation and various verification methods, designers can significantly improve the reliability and quality of their processor designs. The cost of verification is justified by the cost of fixing bugs later on.

Key Topics to Learn for Processor Operation Interview

- Processor Architecture: Understand different processor architectures (e.g., RISC, CISC), their strengths and weaknesses, and how they impact performance.

- Instruction Set Architecture (ISA): Familiarize yourself with common ISAs and their instruction formats. Be prepared to discuss how instructions are fetched, decoded, and executed.

- Pipelining and Parallelism: Grasp the concepts of pipelining and different forms of parallelism (e.g., instruction-level parallelism, data-level parallelism) and their impact on performance.

- Memory Management: Understand virtual memory, caching, and memory hierarchies. Be prepared to discuss their roles in optimizing processor performance and data access.

- Interrupt Handling: Learn how processors handle interrupts, their priority levels, and their impact on program execution. Be ready to discuss different interrupt handling mechanisms.

- Cache Coherence: Understand the challenges of maintaining data consistency in multi-core processors and the mechanisms used to address cache coherence issues.

- Performance Optimization: Explore techniques for optimizing processor performance, including code optimization, compiler optimizations, and hardware-level optimizations.

- Practical Application: Be prepared to discuss how your understanding of processor operation applies to real-world scenarios, such as optimizing code for specific architectures or troubleshooting performance bottlenecks.

- Problem-Solving: Develop your ability to analyze processor-related problems, identify bottlenecks, and propose solutions. Practice working through hypothetical scenarios.

Next Steps

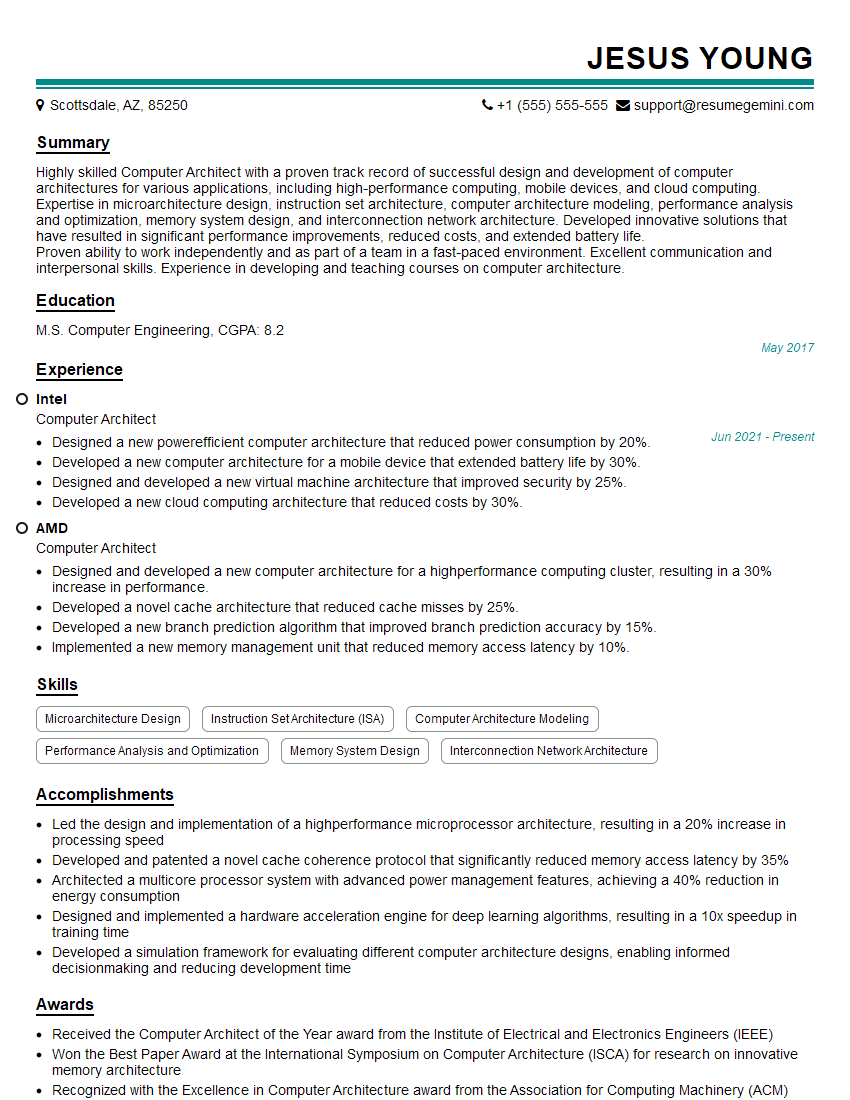

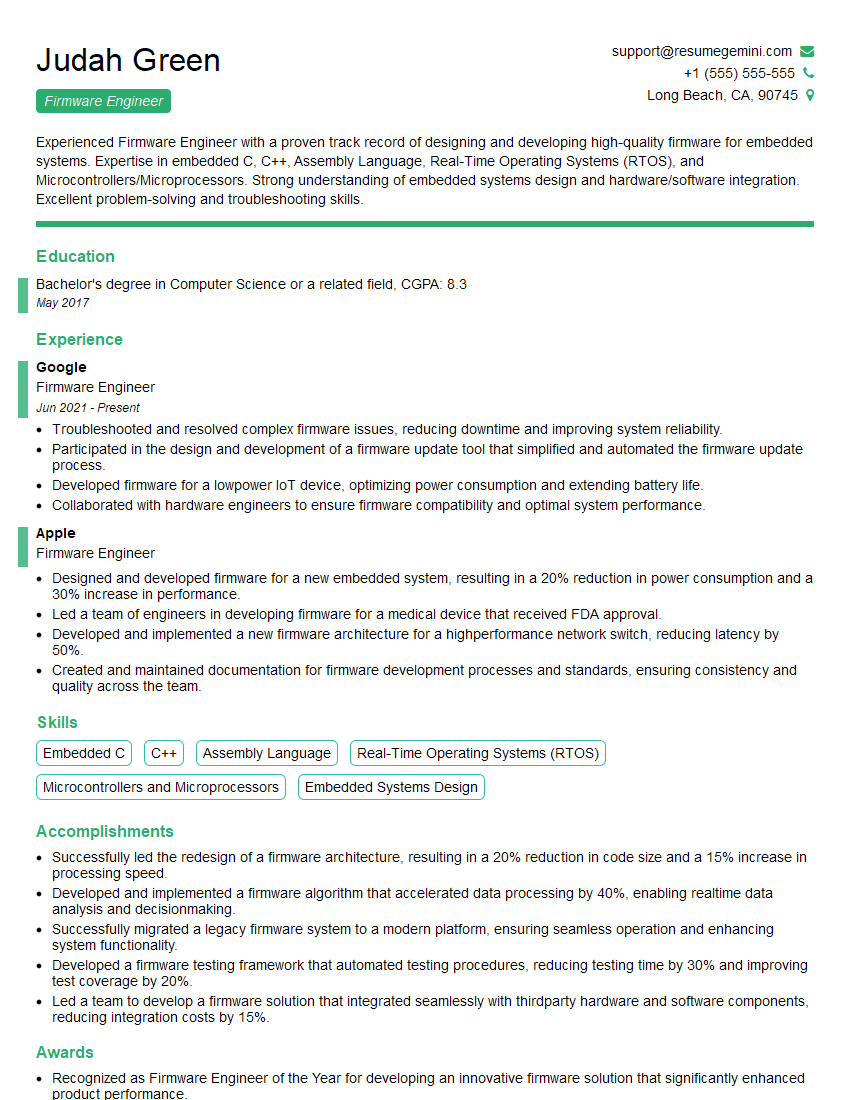

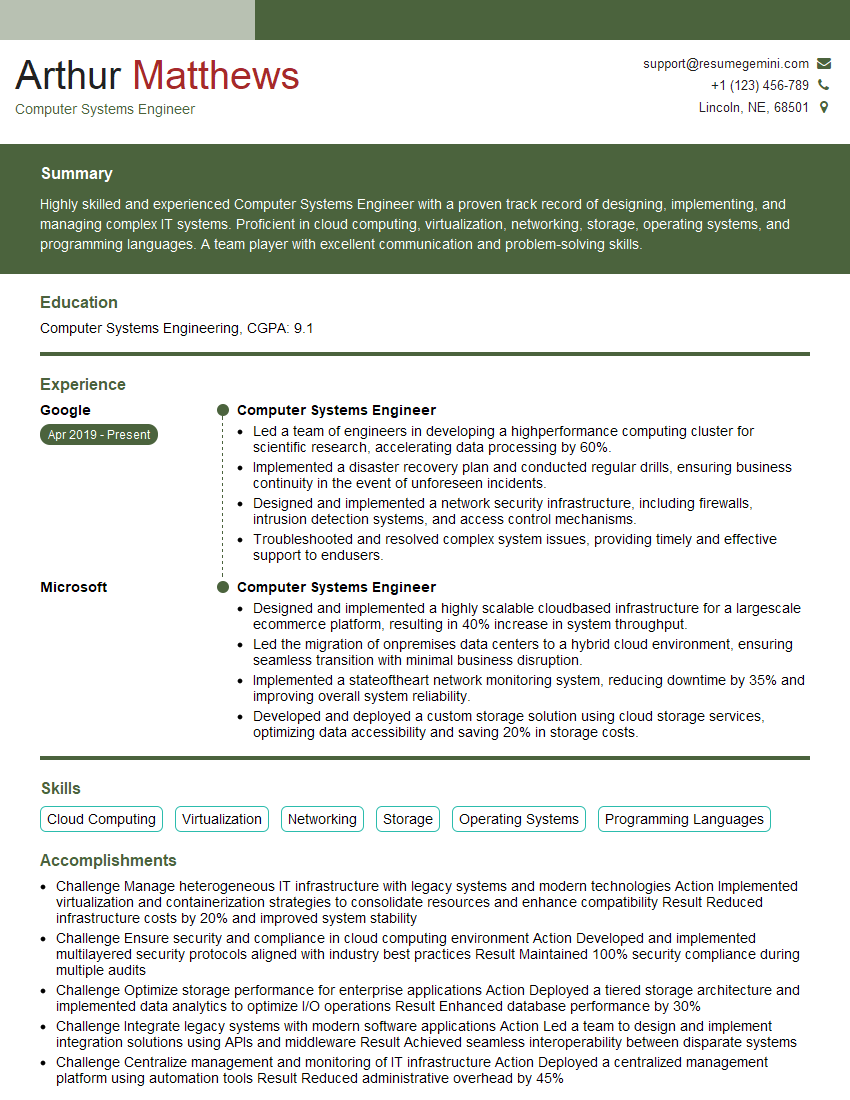

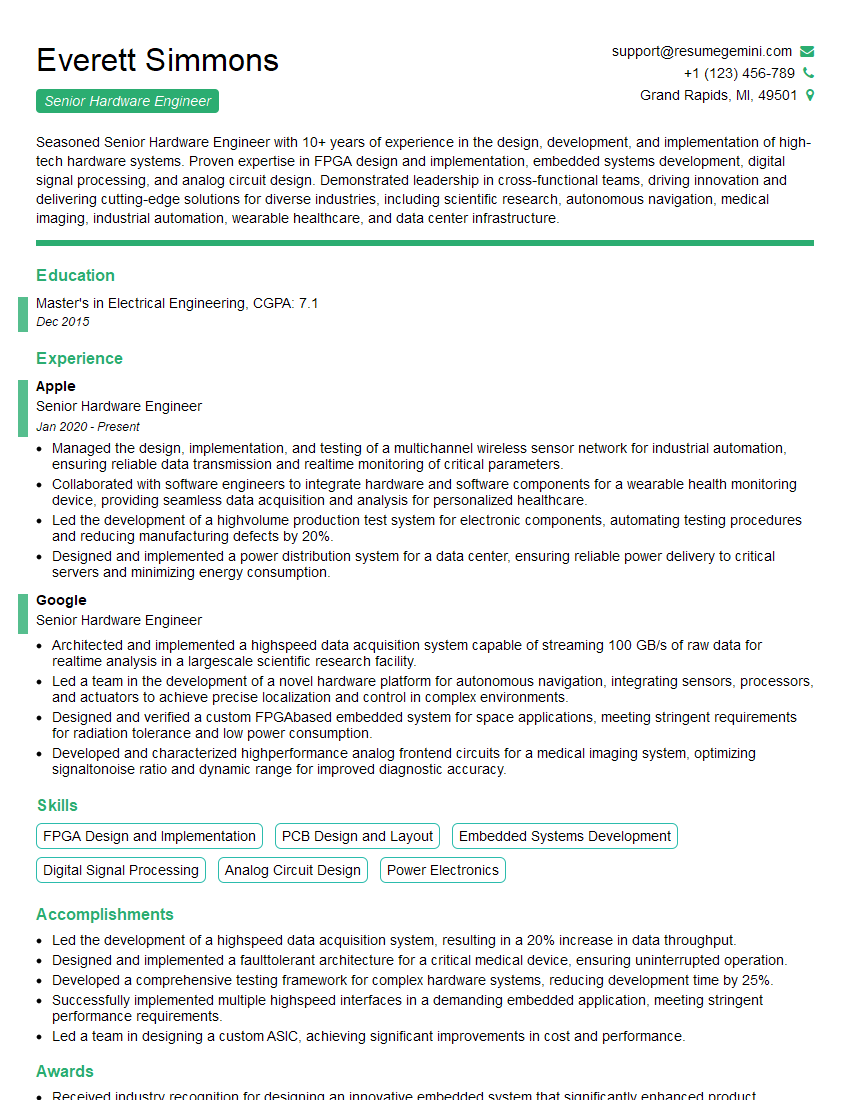

Mastering processor operation is crucial for career advancement in many technology fields, opening doors to exciting opportunities and higher earning potential. A strong understanding of these concepts will significantly enhance your problem-solving skills and technical expertise. To increase your chances of landing your dream job, creating an ATS-friendly resume is essential. ResumeGemini is a trusted resource that can help you build a professional and effective resume that highlights your skills and experience. ResumeGemini provides examples of resumes tailored to processor operation roles, allowing you to craft a compelling document showcasing your qualifications effectively. Invest time in crafting a strong resume – it’s your first impression!

Explore more articles

Users Rating of Our Blogs

Share Your Experience

We value your feedback! Please rate our content and share your thoughts (optional).

What Readers Say About Our Blog

Hello,

We found issues with your domain’s email setup that may be sending your messages to spam or blocking them completely. InboxShield Mini shows you how to fix it in minutes — no tech skills required.

Scan your domain now for details: https://inboxshield-mini.com/

— Adam @ InboxShield Mini

Reply STOP to unsubscribe

Hi, are you owner of interviewgemini.com? What if I told you I could help you find extra time in your schedule, reconnect with leads you didn’t even realize you missed, and bring in more “I want to work with you” conversations, without increasing your ad spend or hiring a full-time employee?

All with a flexible, budget-friendly service that could easily pay for itself. Sounds good?

Would it be nice to jump on a quick 10-minute call so I can show you exactly how we make this work?

Best,

Hapei

Marketing Director

Hey, I know you’re the owner of interviewgemini.com. I’ll be quick.

Fundraising for your business is tough and time-consuming. We make it easier by guaranteeing two private investor meetings each month, for six months. No demos, no pitch events – just direct introductions to active investors matched to your startup.

If youR17;re raising, this could help you build real momentum. Want me to send more info?

Hi, I represent an SEO company that specialises in getting you AI citations and higher rankings on Google. I’d like to offer you a 100% free SEO audit for your website. Would you be interested?

Hi, I represent an SEO company that specialises in getting you AI citations and higher rankings on Google. I’d like to offer you a 100% free SEO audit for your website. Would you be interested?

good