Interviews are opportunities to demonstrate your expertise, and this guide is here to help you shine. Explore the essential ASIC Design interview questions that employers frequently ask, paired with strategies for crafting responses that set you apart from the competition.

Questions Asked in ASIC Design Interview

Q 1. Explain the differences between combinational and sequential logic.

The fundamental difference between combinational and sequential logic lies in their dependence on time. Combinational logic circuits produce outputs that are solely determined by their current inputs. Think of a simple AND gate: the output is HIGH only when both inputs are HIGH; it doesn’t remember past inputs. Sequential logic, on the other hand, incorporates memory elements (like flip-flops) and thus, the output depends not only on the current inputs but also on the past state of the circuit. A simple example is a D flip-flop: its output mirrors the input only when a clock signal transitions, holding the previous value otherwise. This ‘memory’ aspect introduces the concept of time into the system’s behavior.

- Combinational Logic: No memory; output depends only on current inputs. Examples include adders, multipliers, decoders, and encoders.

- Sequential Logic: Contains memory elements; output depends on current inputs and past states. Examples include counters, registers, shift registers, and finite state machines (FSMs).

In ASIC design, understanding this distinction is crucial for efficient design and verification. Choosing the right logic type for a specific function impacts performance, area, and power consumption. For instance, using combinational logic where sequential logic is appropriate might lead to unnecessary complexity and potential timing issues.

Q 2. Describe your experience with different RTL design styles (e.g., behavioral, dataflow, structural).

Throughout my career, I’ve extensively utilized various RTL design styles, tailoring my approach to the specific needs of the project. Behavioral modeling is my go-to for high-level descriptions, particularly when initial performance exploration is paramount. This allows for rapid prototyping and early verification of the algorithm. For instance, I recently modeled a complex FIR filter behaviorally, focusing on the mathematical operations without getting bogged down in implementation details. Later, I refined this with dataflow modeling, specifying data paths and operations explicitly to facilitate optimization. Dataflow excels when dealing with parallel operations and streaming data, leading to more efficient hardware implementation. Finally, structural modeling is used when integrating pre-designed IP blocks, defining connections between them in a hierarchical way.

I’ve found that a blend of these styles is often the most effective. I might start with a high-level behavioral description, then transition to dataflow for critical paths, and conclude with structural modeling for integration. This iterative approach ensures both functional correctness and optimized performance.

Q 3. What are your preferred tools for RTL design and simulation?

My preferred tools for RTL design and simulation are industry standards. For RTL design, I primarily use SystemVerilog, appreciating its powerful features and extensive libraries. It allows for efficient coding and improved verification capabilities compared to older languages like VHDL. For simulation, I rely heavily on ModelSim and QuestaSim, which offer robust debugging and advanced verification capabilities, including functional coverage analysis. These tools provide excellent waveform visualization and sophisticated debugging features, crucial for identifying and resolving design flaws before tapeout. The use of advanced features like assertion-based verification in these simulators significantly improves design quality and confidence. I am also proficient with VCS. The choice often depends on the project requirements and available licensing.

Q 4. How do you handle timing closure in ASIC design?

Timing closure is a critical stage in ASIC design, ensuring that the circuit meets its performance requirements. It’s an iterative process that involves close collaboration between the design and implementation teams. My approach involves a multi-pronged strategy:

- Early Timing Optimization: I focus on writing clean, efficient RTL code, employing techniques like pipelining and clock gating to improve performance.

- Constraint Definition: Creating comprehensive timing constraints is essential. This involves defining clock frequencies, input/output delays, and other timing requirements. The accuracy of these constraints directly impacts the success of timing closure.

- Synthesis Optimization: Using synthesis tools, I explore different optimization options, including area versus speed trade-offs and exploring various synthesis strategies like different optimization levels. Careful selection of synthesis scripts and options is crucial here.

- Static Timing Analysis (STA): Repeated STA runs are essential to identify and resolve timing violations. This includes analyzing setup and hold times, clock skew, and other critical timing parameters.

- Physical Design Collaboration: Close collaboration with the physical design team is crucial. Information about placement, routing, and clock tree synthesis is essential for accurately assessing timing.

- Iterative Refinement: Timing closure is often an iterative process. If violations remain, design changes might be necessary, involving RTL modifications, floorplanning changes, or adjusting clock tree synthesis strategies.

Successfully achieving timing closure requires a thorough understanding of the design, meticulous constraint definition, and a systematic approach to identifying and resolving violations. Experience plays a major role in quickly pinpointing problematic areas.

Q 5. Explain your experience with different synthesis tools and flows.

I possess significant experience with various synthesis tools, including Synopsys Design Compiler, Cadence Genus, and Mentor Graphics Precision Synthesis. My familiarity extends to their respective flows, encompassing constraint specification, optimization strategies, and report analysis. The choice of synthesis tool often depends on project-specific requirements, such as target technology, design complexity, and available licenses. Each tool offers unique features and strengths. For example, Synopsys Design Compiler is widely known for its robust optimization capabilities and extensive library support. Cadence Genus, on the other hand, is valued for its fast synthesis times and efficient power optimization techniques. I’ve utilized the strengths of each tool in different projects, focusing on utilizing advanced optimization options to meet the target performance and area goals. Understanding the intricacies of each tool allows me to effectively address challenges encountered during synthesis and ensure optimized results. A typical flow involves RTL input, constraint definition, synthesis, and report analysis to refine the design.

Q 6. Describe your experience with static timing analysis (STA).

Static Timing Analysis (STA) is indispensable for ensuring the timing correctness of an ASIC design. It’s a crucial part of the verification process and a key factor in achieving timing closure. My experience encompasses performing STA using tools like Synopsys PrimeTime and Cadence Tempus. I’m proficient in interpreting STA reports to identify and resolve timing violations, including setup and hold time violations, clock skew issues, and other critical path delays. STA is not a single step but rather an iterative process that starts early in the design cycle and continues throughout the design flow. The analysis is performed at different stages (post-synthesis, post-PAR) to monitor the impact of various design and implementation choices on timing. For example, I recently used STA to identify and resolve a critical path issue in a high-speed data processing unit. The analysis pinpointed a specific combinational path that was causing setup time violations. By strategically inserting registers to pipeline the path, I successfully resolved the issue and ensured the design met its timing constraints. A solid understanding of STA is vital to guarantee a functionally sound and high-performing ASIC.

Q 7. What are your preferred methods for power optimization in ASIC design?

Power optimization is a critical aspect of modern ASIC design, impacting both cost and performance. My approach to power reduction involves a multi-faceted strategy applied throughout the design cycle:

- RTL Coding Style: Employing efficient RTL coding techniques is fundamental. This includes minimizing glitching, using low-power flip-flops, and employing clock gating where applicable. Careful consideration of data flow and minimizing unnecessary computations are key.

- Power Estimation and Analysis: I rely on power estimation tools to assess power consumption at various stages of the design process, from RTL to post-layout. This provides valuable insight into the power-consuming components and allows for targeted optimization efforts.

- Low-Power Synthesis Options: During synthesis, I utilize specific options aimed at minimizing power consumption without sacrificing performance. Techniques like multiple voltage domains and power gating are effectively employed where feasible.

- Clock Gating: This technique significantly reduces power dissipation in idle circuits by selectively disabling the clock signal to non-critical paths.

- Multi-Voltage Domains: Dividing the design into multiple voltage domains allows for using lower voltages in less critical sections, further reducing power.

- Physical Design Optimization: Working closely with the physical design team, we employ techniques like careful placement and routing to minimize power consumption.

Power optimization is a continuous process that requires careful consideration at every stage of the design flow. The goal is to find the best balance between performance, area, and power consumption. In past projects, applying these techniques has resulted in substantial power savings and improved product longevity.

Q 8. Explain your understanding of low-power design techniques.

Low-power design is crucial for extending battery life in portable devices and reducing energy consumption in data centers. It involves a multi-pronged approach targeting different aspects of the chip’s operation. We aim to minimize both dynamic power (power consumed during switching) and static power (power consumed when idle).

- Voltage Scaling: Reducing the operating voltage directly lowers dynamic power (power ∝ V2). However, this needs careful consideration as it can impact performance and timing.

- Clock Gating: Disabling clock signals to inactive parts of the circuit eliminates unnecessary switching activity and reduces dynamic power. This is often implemented using logic to control clock enable signals.

- Power Gating: Completely isolating power to inactive blocks. This is a more aggressive technique than clock gating, achieving larger power savings but potentially introducing latency during activation.

- Multi-VDD Design: Employing different voltage domains for different parts of the chip. Critical performance sections might operate at a higher voltage, while less critical parts operate at a lower voltage.

- Architectural Optimization: Designing the architecture itself to minimize power consumption. This includes choosing appropriate algorithms, data structures, and communication protocols.

- Leakage Current Reduction: Minimizing the current that leaks even when the circuit is not actively switching. This is achieved through careful transistor sizing and process technology selection.

For example, in a mobile processor, clock gating might be used to disable the GPU when not in use, while power gating might be applied to less frequently accessed memory controllers. Multi-VDD might be used to supply the high-performance cores at a higher voltage than the memory interfaces.

Q 9. Describe your experience with clock domain crossing (CDC) and its challenges.

Clock domain crossing (CDC) refers to the situation where signals are transferred between different clock domains in an ASIC. This presents significant challenges as the relative timing between the clocks can be unpredictable, leading to metastability issues.

Metastability is a state where a flip-flop’s output is neither a clear ‘0’ nor a clear ‘1’, but rather an indeterminate value. This can lead to unpredictable behavior and system malfunction. The key to handling CDC is careful design and verification.

- Synchronization Techniques: Using multiple flip-flops in series to reduce the probability of metastability. The more flip-flops, the lower the probability but at the cost of latency.

- Asynchronous FIFOs: These are specially designed FIFOs (First-In, First-Out) buffers that handle data transfer between asynchronous domains. They provide robust synchronization and error detection mechanisms.

- Gray Codes: Using Gray codes for encoding counter values can reduce the number of bit changes in the signal, minimizing the risk of metastability when crossing clock domains.

In my experience, failing to properly handle CDC can lead to intermittent and difficult-to-debug system failures. I’ve used asynchronous FIFOs extensively in high-speed data interfaces, implementing rigorous synchronization schemes with multiple stages of flip-flops to mitigate metastability risks.

Q 10. How do you approach the verification of an ASIC design?

ASIC verification is a rigorous process ensuring the design functions as intended. It’s not just about finding bugs; it’s about proving the design meets its specifications with high confidence. My approach involves a multi-level strategy that combines different verification methodologies:

- Unit Verification: Verifying individual components or modules independently.

- Integration Verification: Verifying the interaction between different modules after integration.

- System Verification: Verifying the entire system against its complete specifications.

Each level uses a combination of techniques such as simulation, formal verification, and emulation. I typically begin with a comprehensive test plan outlining the scope of verification, specific test cases, and coverage metrics. Then, we systematically execute and analyze the results, iteratively refining the test plan based on uncovered bugs and any incomplete coverage areas. Regression testing is essential to ensure new modifications don’t introduce regressions.

Q 11. What are your preferred verification methodologies (e.g., UVM, OVM)?

I have extensive experience with the Universal Verification Methodology (UVM) and have also worked with OVM in the past. UVM is my preferred methodology due to its reusability, scalability, and industry-wide adoption. It provides a well-defined framework for creating robust and maintainable verification environments.

UVM’s features, such as its component-based architecture, transaction-level modeling (TLM), and sophisticated reporting mechanisms, greatly improve verification efficiency and coverage. The ability to reuse testbenches across different projects saves considerable time and resources. For example, a UVM environment for a specific communication protocol can be adapted and reused for various designs incorporating that protocol.

While OVM provided a good foundation, UVM offers significant improvements in terms of standardization, features, and community support.

Q 12. Explain your experience with formal verification.

Formal verification uses mathematical techniques to prove the correctness of a design against its specification. Unlike simulation, which tests a limited set of scenarios, formal verification can explore all possible states within a defined scope, providing a more comprehensive analysis.

I have used formal verification to prove the absence of certain design errors, such as deadlocks, assertion violations, and timing violations. Formal verification is particularly useful for verifying complex control logic and data paths, where exhaustive simulation would be computationally infeasible. For example, I used formal methods to verify a complex state machine responsible for handling memory transactions in a high-bandwidth memory controller.

The key to successful formal verification is careful specification writing. A poorly written specification will make it difficult, if not impossible, to verify the design.

Q 13. Describe different types of ASIC testing and their purposes (e.g., functional, DFT).

ASIC testing is crucial to ensure the manufactured chips function correctly. Different testing types serve distinct purposes:

- Functional Testing: Verifies the design’s functionality against its specifications, often using simulation or emulation-based techniques. This checks if the design works as expected under various operating conditions.

- DFT (Design for Testability): Adds extra circuitry to the design to improve testability, making it easier to detect faults during manufacturing testing. Techniques include scan chains, boundary scan (JTAG), and built-in self-test (BIST).

- Manufacturing Test: This is performed on the manufactured chips to identify faulty units before they are shipped to customers. It uses automated test equipment (ATE) to apply test patterns and evaluate the responses.

- Reliability Testing: Evaluates the chip’s ability to withstand various environmental stresses, such as temperature extremes, voltage variations, and radiation.

In a project I worked on, we utilized scan chains for DFT to enable efficient testing of the internal logic. This reduced the test time significantly, improving manufacturing yield and reducing overall costs.

Q 14. How do you handle design for testability (DFT)?

Design for Testability (DFT) is an essential aspect of ASIC design. It involves incorporating mechanisms to make the chip easier to test after manufacturing. My approach integrates DFT considerations early in the design process.

- Scan Chain Insertion: Replacing internal flip-flops with scannable flip-flops that can be chained together for easy testing. This allows sequential access to internal nodes to check their states.

- Boundary Scan (JTAG): Using a standard interface (JTAG) to access and test boundary cells, simplifying the testing of the chip’s external connections.

- Built-in Self-Test (BIST): Implementing circuitry that allows the chip to test itself, eliminating the need for external test equipment in some cases. This reduces testing time and cost.

- ATPG (Automatic Test Pattern Generation): Using ATPG tools to generate efficient test patterns to detect as many faults as possible.

For example, in a large processor design, we used a combination of scan chains and JTAG to allow for complete test coverage. We also incorporated BIST into specific modules to reduce testing time and complexity. The early integration of DFT significantly reduced the overall test cost and improved manufacturing yield.

Q 15. What is your experience with scan-based testing?

Scan-based testing is a crucial technique for verifying the functionality of an ASIC after fabrication. It involves adding dedicated scan chains to the design, allowing us to control and observe the state of individual flip-flops. Imagine it like a long chain where each link represents a flip-flop. We can serially shift test data into the chain, apply a clock, and then shift out the results to verify the correct operation of the logic between flip-flops. This dramatically improves fault coverage compared to traditional methods, because we can test internal nodes that are not easily accessible through primary inputs and outputs.

My experience includes extensive use of scan-based testing methodologies across various projects. I’ve worked with different scan architectures, such as full scan and partial scan, optimizing the chain length and minimizing the area overhead. I’m proficient in using ATPG (Automatic Test Pattern Generation) tools to generate test vectors and analyzing fault coverage reports to identify and address any weaknesses in our test strategy. For example, on a recent project involving a high-speed network processor, we employed a combination of full and partial scan to achieve 99.5% fault coverage while keeping the area impact within acceptable limits. This process involved careful analysis of the design’s critical paths and the strategic placement of scan chains to maximize efficiency.

Career Expert Tips:

- Ace those interviews! Prepare effectively by reviewing the Top 50 Most Common Interview Questions on ResumeGemini.

- Navigate your job search with confidence! Explore a wide range of Career Tips on ResumeGemini. Learn about common challenges and recommendations to overcome them.

- Craft the perfect resume! Master the Art of Resume Writing with ResumeGemini’s guide. Showcase your unique qualifications and achievements effectively.

- Don’t miss out on holiday savings! Build your dream resume with ResumeGemini’s ATS optimized templates.

Q 16. Explain your understanding of physical design aspects like placement and routing.

Physical design encompasses the process of transforming a logically correct netlist into a physically realizable layout on a silicon die. Placement and routing are the two most critical steps. Placement involves strategically positioning the logic cells and macros on the die to optimize area, timing, and power consumption. Think of it like arranging pieces of a jigsaw puzzle, but with constraints related to connectivity, power delivery, and timing requirements. Routing involves creating electrical connections between these cells using metal layers, ensuring signal integrity and adhering to design rule checks (DRC).

My experience includes working with advanced placement and routing algorithms, using tools that employ techniques like simulated annealing and detailed routing optimizations. For instance, I’ve utilized techniques like clock tree synthesis (CTS) to ensure consistent clock arrival across the chip, which is vital for proper operation. In one project, I improved the critical path timing by 15% by using a combination of optimized placement and advanced routing techniques, ultimately leading to a higher frequency design.

Q 17. How do you ensure signal integrity in high-speed ASIC designs?

Signal integrity in high-speed ASIC designs is paramount to avoid signal degradation and ensure reliable operation. High-speed signals are susceptible to various effects like reflections, crosstalk, and electromagnetic interference (EMI). To mitigate these, we employ several techniques. First, proper signal routing is crucial, including the use of controlled impedance traces and proper spacing between signals to minimize crosstalk. We also employ techniques such as shielding and grounding planes to minimize EMI.

Advanced techniques like eye diagram analysis, simulation using tools like HSPICE, and equalization are used to verify signal integrity. I’ve used these techniques extensively to identify and resolve signal integrity issues. For example, in a high-speed serial link design, I used simulations to identify and mitigate reflections caused by impedance mismatch at the connector, resulting in a significantly improved bit-error rate (BER).

Q 18. Describe your experience with different physical design tools.

I have extensive experience with leading physical design tools, including Synopsys IC Compiler, Cadence Innovus, and Mentor Graphics Olympus-SoC. Each tool has its strengths and weaknesses; for example, IC Compiler excels in its advanced placement capabilities, while Innovus offers robust routing algorithms. My experience extends to using these tools across the entire flow, from floorplanning and placement to routing, clock tree synthesis, and physical verification. I am comfortable with various methodologies, such as hierarchical design and mixed-signal flows.

The choice of tool often depends on the project requirements and the team’s expertise. In one project, we used Synopsys IC Compiler for its powerful congestion-aware routing, leading to a more efficient chip layout. In another, we leveraged Cadence Innovus’s advanced timing analysis features for critical path optimization. This flexibility makes me adaptable to different project demands and allows me to leverage the strengths of various industry-standard tools. This adaptability to use different tools effectively is part of what makes me a successful physical design engineer.

Q 19. What are your strategies for managing complexity in large ASIC designs?

Managing complexity in large ASIC designs requires a structured approach. We use hierarchical design methodologies, breaking down the design into smaller, manageable blocks. This allows multiple teams to work concurrently and simplifies verification. Furthermore, employing formal verification techniques, such as model checking, aids in catching subtle design errors early in the process.

Effective communication and collaboration are also crucial. Clear documentation, regular design reviews, and the use of version control systems like Git are indispensable. For example, on a recent project involving a complex multi-core processor, we utilized a hierarchical design methodology, dividing the processor into core units, cache subsystems, and interconnects. Each unit was designed and verified independently, and the integration was done systematically, reducing the risk of complex integration issues. This methodical approach, along with rigorous verification, allowed us to successfully deliver a complex design on schedule.

Q 20. How do you handle design trade-offs between area, power, and performance?

The design trade-off between area, power, and performance is a constant challenge in ASIC design. Often, improving one aspect necessitates compromises in others. For instance, increasing the clock frequency improves performance but can lead to higher power consumption and potentially increased area. Similarly, minimizing area might lead to performance degradation or increased power consumption.

Managing these trade-offs involves careful analysis and optimization techniques. For instance, power optimization techniques like clock gating and power gating can significantly reduce power consumption without impacting performance too severely. Careful selection of standard cells and libraries is also essential. Ultimately, the optimal balance depends on the specific application requirements. In one project, we were able to reduce the area by 10% by using a lower-power standard cell library with only a minor impact on performance, thus optimizing for power efficiency. This was a critical decision based on the project’s requirements.

Q 21. Explain your experience with scripting languages (e.g., Perl, Python, TCL).

Scripting languages are essential for automating tasks and improving efficiency in ASIC design. I’m proficient in Perl, Python, and TCL. Perl is particularly useful for complex text processing and data manipulation tasks, while Python offers a broader range of libraries and tools for data analysis and visualization. TCL is heavily used in most EDA tools for automating design flows.

I use these languages to automate various tasks, such as generating design reports, managing design files, automating verification flows, and customizing EDA tool flows. For example, I wrote a Python script to automate the generation of timing reports and extract critical path information, providing a clear overview of timing performance and identifying areas for improvement. This dramatically reduced manual effort and improved the turnaround time of the design process. This automation ability significantly improves our productivity and reduces human error.

Q 22. How do you manage version control in an ASIC design project?

Version control is paramount in ASIC design, where even minor changes can have significant ripple effects. We typically use Git, a distributed version control system, for its robustness and collaborative features. Each design file, from RTL code to testbenches and scripts, is meticulously tracked. We establish a clear branching strategy, often using a combination of feature branches and release branches. Feature branches allow developers to work on individual components concurrently without disrupting the main codebase. Once a feature is complete and tested, it’s merged into the main branch via a pull request, triggering a thorough code review process. This ensures code quality and prevents integration issues. For example, a team member might create a branch to implement a new algorithm for a specific module; this work happens isolated from the main branch until it’s fully tested and ready for integration. The history is meticulously maintained, allowing us to easily revert to previous versions if necessary, a crucial aspect when dealing with complex designs and potential bugs.

We also utilize a robust change management process, often integrated with our version control system, to track and document changes. This includes descriptions, author information, and the specific impact of each change. This comprehensive record aids in debugging, tracing design evolution, and ensuring accountability. Think of it like a detailed design journal where every modification is meticulously logged and versioned for easy retrieval and analysis.

Q 23. Describe your experience with different design methodologies (e.g., top-down, bottom-up).

My experience encompasses both top-down and bottom-up design methodologies, each with its strengths and weaknesses. In a top-down approach, we start with the high-level system specification and progressively decompose it into smaller, manageable blocks. This facilitates early verification of system-level functionality but can sometimes lead to challenges in the detailed implementation phase if initial specifications aren’t well-defined. Imagine designing a car; top-down would start with the car’s overall design and gradually work on the engine, chassis, and other components.

Conversely, the bottom-up approach focuses on developing and verifying individual modules first, before integrating them into larger blocks. This method excels in managing complexity and allows for detailed optimization of individual components. However, it can be more challenging to ensure the seamless integration of independently developed modules and potentially miss higher-level system-level issues. Think of building the car engine first, then the chassis, and only then integrating them; this is the bottom-up approach.

In practice, a hybrid approach, often employing a combination of top-down decomposition and bottom-up verification, is commonly used. This balances the advantages of both methodologies while mitigating their limitations, leading to a more efficient and robust design process.

Q 24. Explain your understanding of different memory architectures.

Memory architectures are a crucial aspect of ASIC design, impacting performance and power consumption significantly. I’m familiar with various architectures, including:

- SRAM (Static Random-Access Memory): Fast, relatively low power consumption when active, but higher standby power. Used extensively in caches and registers.

- DRAM (Dynamic Random-Access Memory): Higher density and lower cost per bit than SRAM, but slower and requires periodic refresh. Commonly used for main memory.

- ROM (Read-Only Memory): Non-volatile memory used to store firmware or configuration data. Data is programmed during fabrication and cannot be changed easily.

- Flash Memory: Non-volatile memory with higher endurance and density than ROM, commonly used for boot code storage or data logging. Writing is slower than reading.

- Embedded Memory: Memory integrated directly within the ASIC, often customized for specific applications to optimize performance and reduce power consumption.

Choosing the right memory architecture requires careful consideration of factors such as access speed, power consumption, density, cost, and non-volatility. For example, a high-performance computing ASIC might use a large amount of fast SRAM for caching, while a low-power embedded system might employ lower-density flash memory for data storage. The optimal choice depends on the specific application requirements.

Q 25. Describe your experience with different bus protocols (e.g., AXI, APB).

I have extensive experience with various bus protocols, primarily AXI (Advanced eXtensible Interface) and APB (Advanced Peripheral Bus). AXI is a high-performance, widely adopted bus protocol in modern SoCs, supporting high-bandwidth data transfers and efficient burst transactions. Its flexible architecture enables efficient communication between different components, such as processors, memory controllers, and peripherals. It’s particularly useful in complex systems needing high throughput.

APB, on the other hand, is a lower-bandwidth, simpler protocol ideal for connecting low-speed peripherals such as GPIOs and timers. Its lightweight nature makes it power-efficient. Imagine AXI as a high-speed expressway for large data movements, while APB is a local road for slow, steady traffic. Choosing between them depends entirely on the data rate and complexity of the interface.

My experience extends to integrating these protocols into designs, implementing arbitration logic, and optimizing data transfer efficiency. I understand the nuances of burst transfers, data widths, and address mapping to ensure efficient communication between different blocks within the system. I’ve also worked with other protocols like Wishbone in smaller, simpler projects.

Q 26. How do you debug complex ASIC design issues?

Debugging complex ASIC design issues requires a systematic approach. It starts with a thorough understanding of the design specifications and a clear definition of the observed problem. We begin with simulation. We use various simulation tools to reproduce the failure and pinpoint the root cause at the RTL level. This involves examining waveforms, tracing signals, and checking timing constraints.

If simulations don’t resolve the issue, we move to post-silicon debugging, leveraging tools like logic analyzers and JTAG debuggers to analyze the behavior of the chip on the board. The use of assertions and coverage metrics within the design is very valuable in narrowing down the failure locations. Sometimes, we might use techniques like power analysis to identify power consumption anomalies linked to specific blocks.

A crucial aspect is effective communication and collaboration. I’ve found that regular team meetings, code reviews, and the use of shared debugging tools and documentation significantly accelerate the process. This systematic approach, which combines simulation, post-silicon analysis, and collaborative teamwork, is extremely effective in resolving even the most intricate design problems. I’ve even had success using formal verification tools in very complex designs to mathematically prove the correctness of certain circuits, avoiding the need for exhaustive simulation.

Q 27. Describe your experience with working within a team on a large ASIC project.

I have extensive experience working in large, multidisciplinary teams on significant ASIC projects. Effective teamwork is critical for success, and my approach is built on clear communication, defined roles, and a collaborative work environment. We typically use project management tools to track progress, manage tasks, and ensure everyone remains synchronized. I’ve worked in teams employing Agile methodologies, leading to iterative development and quicker feedback cycles. This allows for flexibility and quicker adaptation to changing requirements.

I actively contribute to team discussions, offering technical expertise and proactively addressing potential roadblocks. I value open communication and believe that by fostering an inclusive environment, we can leverage the diverse strengths of team members. For example, on one project, I took the lead in mentoring junior engineers and resolving conflicts effectively. This enabled us to deliver a complex ASIC on time and within budget.

In larger projects, the modular nature of ASIC design often dictates that individuals, or smaller groups, work on discrete aspects of the larger design. Collaboration then centers on the clear definition of interfaces and the regular verification of integration points between these modules.

Q 28. Explain your familiarity with relevant industry standards (e.g., IEEE standards).

I’m well-versed in relevant industry standards, including various IEEE standards crucial for ASIC design. These standards govern various aspects of design, verification, and testing, ensuring interoperability and reliability. For example, I’m familiar with:

- IEEE 1800: SystemVerilog, the hardware description language (HDL) used to design and model ASICs.

- IEEE 1364: Verilog, another HDL used in ASIC design, though SystemVerilog is becoming more prevalent.

- IEEE 1149.1 (JTAG): Standard for boundary-scan testing, widely used for testing and debugging ASICs.

- Various standards related to bus protocols: AXI, AMBA etc.

Adherence to these standards is not merely a matter of compliance; it directly impacts the quality, reliability, and testability of the design. Utilizing standardized interfaces and methodologies enhances collaboration and reduces integration challenges. These standards create a common language and framework that helps mitigate potential ambiguities and improve overall design quality.

Key Topics to Learn for ASIC Design Interview

- Digital Logic Design Fundamentals: Mastering Boolean algebra, logic gates, combinational and sequential circuits is crucial. Understand how these concepts translate into real-world applications within ASICs.

- Verilog/SystemVerilog: Proficiency in HDL coding is essential. Practice designing modules, writing testbenches, and understanding simulation results. Consider exploring advanced concepts like UVM (Universal Verification Methodology).

- Synthesis and Optimization: Learn the process of translating HDL code into a gate-level netlist. Understand different optimization techniques and their impact on power, performance, and area (PPA).

- Timing Analysis and Closure: Grasp the concepts of setup and hold time violations, clock domain crossing, and various techniques for timing closure. This is a critical area for practical ASIC design.

- Physical Design and Implementation: Familiarize yourself with the flow from synthesis to routing, including floorplanning, placement, and routing. Understand the challenges and trade-offs involved.

- Low-Power Design Techniques: Explore different low-power design methodologies and techniques to optimize power consumption in ASICs, a crucial aspect for modern designs.

- Verification Methodologies: Understand various verification techniques, including simulation, formal verification, and emulation. This is critical for ensuring the functionality and reliability of your designs.

- Memory Architectures and Design: Learn about different types of memories (SRAM, DRAM, etc.) and how to effectively integrate them into ASIC designs.

- Advanced Topics (Optional but beneficial): Consider exploring topics like high-speed interfaces (e.g., PCIe, SerDes), embedded systems, and security considerations in ASIC design.

Next Steps

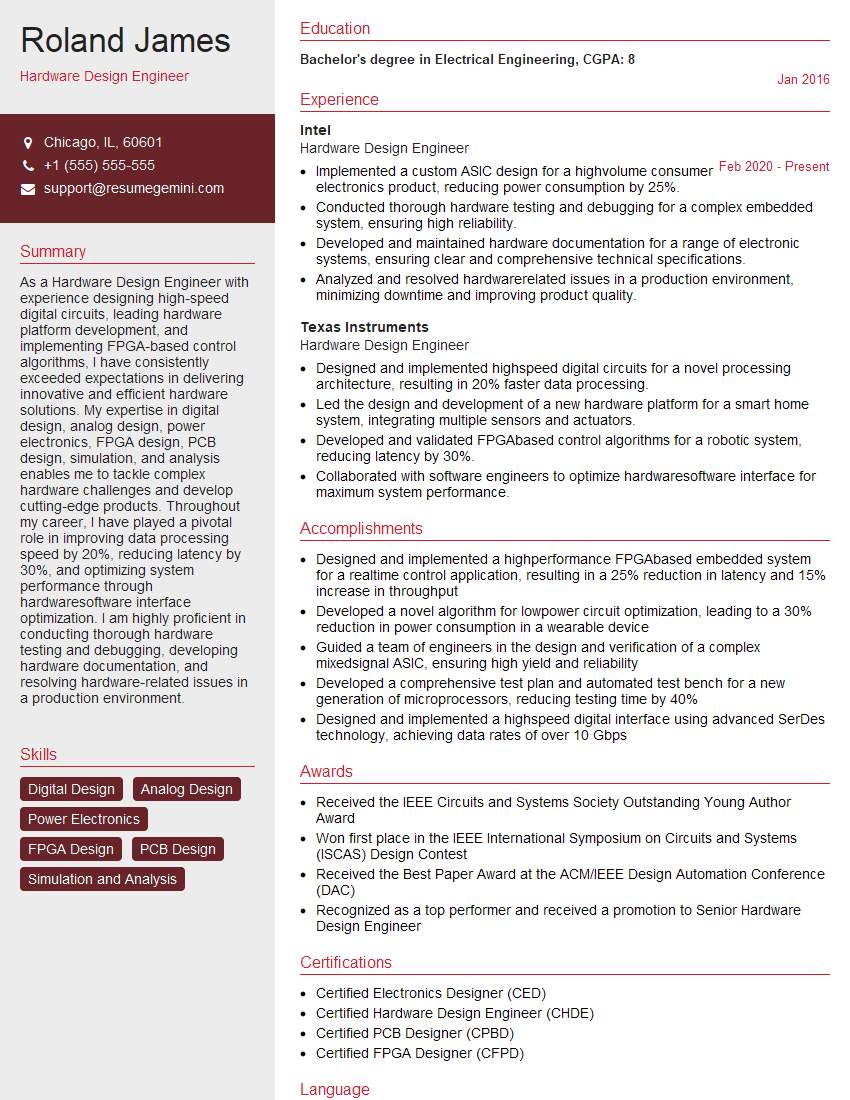

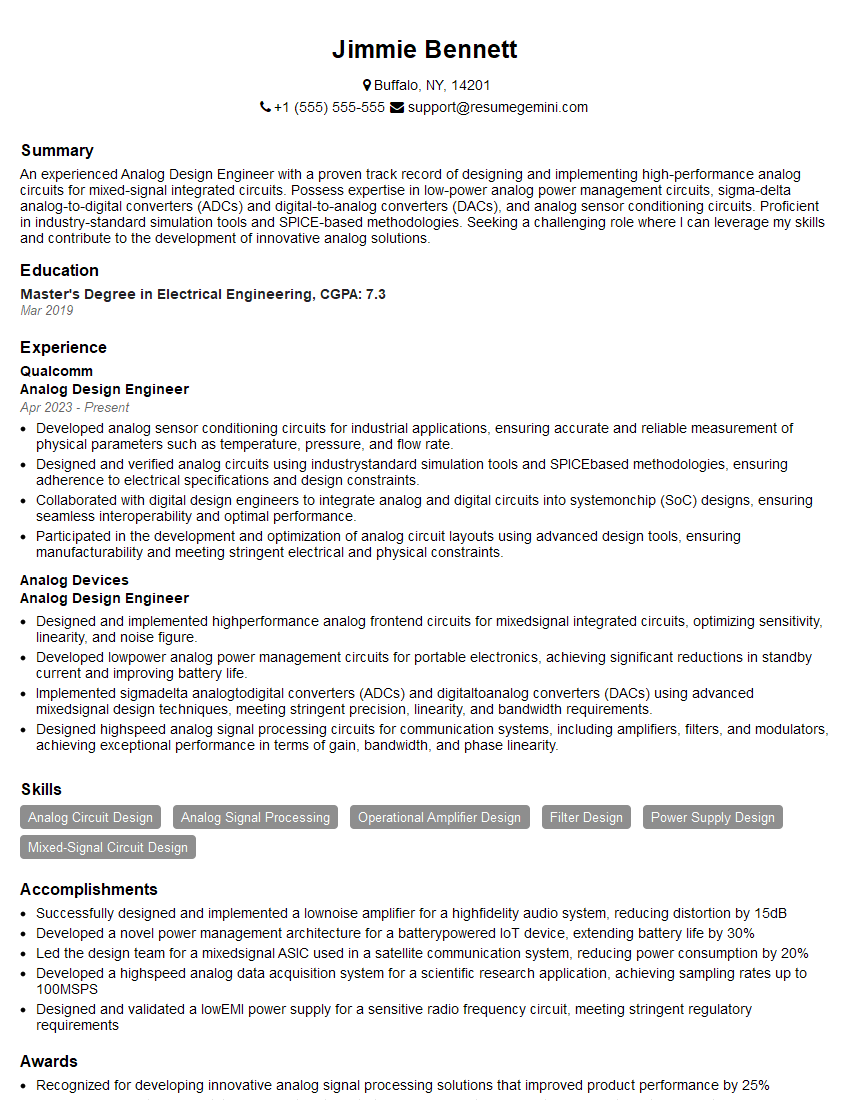

Mastering ASIC design opens doors to a rewarding career with significant growth potential in a constantly evolving technological landscape. Landing your dream role requires a compelling resume that showcases your skills and experience effectively. Creating an ATS-friendly resume is crucial for getting past Applicant Tracking Systems and into the hands of hiring managers. We highly recommend leveraging ResumeGemini to build a professional and impactful resume tailored to the ASIC design industry. ResumeGemini provides examples of resumes specifically designed for ASIC Design roles, helping you craft a document that highlights your unique qualifications and experience. Invest in your future and take the next step towards your ASIC design career today!

Explore more articles

Users Rating of Our Blogs

Share Your Experience

We value your feedback! Please rate our content and share your thoughts (optional).

What Readers Say About Our Blog

Hello,

We found issues with your domain’s email setup that may be sending your messages to spam or blocking them completely. InboxShield Mini shows you how to fix it in minutes — no tech skills required.

Scan your domain now for details: https://inboxshield-mini.com/

— Adam @ InboxShield Mini

Reply STOP to unsubscribe

Hi, are you owner of interviewgemini.com? What if I told you I could help you find extra time in your schedule, reconnect with leads you didn’t even realize you missed, and bring in more “I want to work with you” conversations, without increasing your ad spend or hiring a full-time employee?

All with a flexible, budget-friendly service that could easily pay for itself. Sounds good?

Would it be nice to jump on a quick 10-minute call so I can show you exactly how we make this work?

Best,

Hapei

Marketing Director

Hey, I know you’re the owner of interviewgemini.com. I’ll be quick.

Fundraising for your business is tough and time-consuming. We make it easier by guaranteeing two private investor meetings each month, for six months. No demos, no pitch events – just direct introductions to active investors matched to your startup.

If youR17;re raising, this could help you build real momentum. Want me to send more info?

Hi, I represent an SEO company that specialises in getting you AI citations and higher rankings on Google. I’d like to offer you a 100% free SEO audit for your website. Would you be interested?

Hi, I represent an SEO company that specialises in getting you AI citations and higher rankings on Google. I’d like to offer you a 100% free SEO audit for your website. Would you be interested?

good