Feeling uncertain about what to expect in your upcoming interview? We’ve got you covered! This blog highlights the most important Component Verification interview questions and provides actionable advice to help you stand out as the ideal candidate. Let’s pave the way for your success.

Questions Asked in Component Verification Interview

Q 1. Explain your understanding of UVM (Universal Verification Methodology).

UVM, or Universal Verification Methodology, is a standard verification methodology based on SystemVerilog. Think of it as a well-organized toolbox filled with reusable components and best practices for building robust and efficient verification environments. It’s built upon object-oriented programming principles, which makes it highly modular, reusable, and scalable.

Key components of UVM include:

- Factory: Allows for easy swapping of components without modifying the main testbench.

- Transaction-Level Modeling (TLM): Enables efficient communication between different components of the testbench, reducing simulation time.

- Sequences and Drivers: Manage stimulus generation and transaction sequencing.

- Monitors and Scoreboards: Observe DUT (Device Under Test) activity and compare it against expected results.

- Agents: Combine drivers, monitors, and sequences into a cohesive unit.

In a real-world project, imagine verifying a complex processor. Using UVM, we could create separate agents for different processor buses, each with their own drivers, monitors, and sequences. The factory would allow us to easily switch between different configurations for various tests. This modularity significantly improves maintainability and reduces debugging time compared to a traditional, flat testbench.

Q 2. What is the difference between verification and validation?

Verification and validation are often confused, but they are distinct processes. Think of building a house: verification is making sure the house is built according to the blueprints (specifications), while validation is making sure the house meets the needs of the homeowner (requirements).

Verification focuses on ensuring the design implementation matches the design specification. It involves techniques like simulation, formal verification, and emulation to prove the design is functionally correct.

Validation focuses on ensuring the design meets the overall system requirements. It involves activities like system-level testing, integration testing, and user acceptance testing to verify the design meets the intended purpose.

For example, verification might prove that a particular adder circuit adds two numbers correctly according to its specification. Validation, however, would assess whether the entire processor, including that adder, meets the performance and power requirements of the target application.

Q 3. Describe your experience with SystemVerilog and its use in verification.

SystemVerilog is my primary hardware description and verification language. It’s an extension of Verilog, offering advanced features crucial for building complex verification environments. Its object-oriented programming capabilities, along with features like constraints, random stimulus generation, and assertions, are invaluable.

I’ve extensively used SystemVerilog to:

- Create UVM testbenches: Building reusable and scalable verification environments using classes, interfaces, and virtual interfaces.

- Develop constrained-random test cases: Generating diverse stimulus to thoroughly exercise the design, significantly improving coverage.

- Implement checkers and scoreboards: Verifying the correctness of the DUT’s behavior using sophisticated assertion mechanisms.

- Perform functional coverage analysis: Tracking the progress of verification and identifying untested areas.

For instance, in a recent project involving a networking chip, I used SystemVerilog to create a UVM environment that generated random network packets with various constraints, monitored the chip’s response, and checked for protocol compliance using assertions. This significantly improved our verification efficiency and coverage.

Q 4. How do you handle testbench development and management?

Testbench development and management require a structured approach. I typically follow these steps:

- Planning and Design: Defining the verification plan, identifying key features to verify, and designing the overall testbench architecture.

- Modular Design: Building the testbench using reusable components to improve maintainability and scalability. UVM is instrumental in this process.

- Version Control: Using a version control system like Git to track changes, manage different versions, and collaborate effectively.

- Regression Testing: Running the test suite regularly to ensure that new code doesn’t break existing functionality.

- Coverage Analysis: Monitoring code coverage, functional coverage, and assertion coverage to measure the completeness of verification.

- Defect Tracking: Using a defect tracking system to record and track bugs found during verification.

In my experience, a well-planned and managed testbench significantly reduces time to market and improves the overall quality of the design.

Q 5. What are your preferred code coverage metrics and why?

My preferred code coverage metrics are statement coverage, branch coverage, and toggle coverage. These provide a good balance between ease of implementation and effectiveness in identifying untested parts of the design.

Statement coverage measures the percentage of code statements executed during simulation. While simple to obtain, it doesn’t capture all possible execution paths.

Branch coverage tracks the execution of each branch (if-else, case) in the design, offering better coverage than statement coverage.

Toggle coverage measures the transitions (0 to 1 and 1 to 0) of signals, identifying potential logic failures related to signal changes. This is particularly useful for designs with asynchronous behavior.

I also often use functional coverage, which is more design-specific and focuses on verifying features and functionalities rather than lines of code. This complements the code coverage metrics, giving a more holistic picture of the verification completeness.

Q 6. Explain your experience with assertion-based verification.

Assertion-based verification is a powerful technique that allows us to specify expected behavior directly within the design or testbench using formal assertions. Think of assertions as formal checks built into the design, constantly monitoring whether specific conditions are met during simulation. This dramatically improves the efficiency and effectiveness of the verification process by catching errors early.

I have used assertions to:

- Verify data integrity: Checking for data corruption or unexpected values.

- Ensure protocol compliance: Validating adherence to communication protocols.

- Monitor timing constraints: Detecting timing violations.

For example, in a recent project verifying a memory controller, I implemented assertions to check for data consistency after read and write operations. This automatically flagged any memory corruption errors, significantly shortening the debugging process. Assertions provide immediate feedback, unlike traditional scoreboard-based verification that might only identify errors at the end of the simulation.

Q 7. Describe your experience with different verification methodologies (e.g., OVM, VMM).

While UVM is my primary methodology, I have experience with other methodologies, including OVM (Open Verification Methodology) and VMM (Verification Methodology Manual). OVM was a predecessor to UVM, sharing many similarities in its object-oriented approach. VMM, on the other hand, offers a more procedural approach.

The core difference lies in their implementation and approach to building the verification environment. UVM provides a more robust and standardized framework with features like the factory pattern and TLM, making it more efficient and scalable for complex projects. While OVM and VMM served their purposes, UVM has largely become the industry standard due to its improved features and widespread adoption.

My experience with these different methodologies has provided me with a broad understanding of verification techniques and the ability to adapt to various project requirements and team preferences. The underlying principles of modularity, reusability, and constrained random verification remain consistent across all methodologies.

Q 8. How do you debug complex verification failures?

Debugging complex verification failures requires a systematic approach. It’s like detective work, piecing together clues to find the root cause. I start by thoroughly examining the error messages and logs, focusing on the timing and sequence of events leading up to the failure. This often involves using a debugger to step through the code and inspect variables.

Next, I employ waveform visualization tools to analyze signals and identify discrepancies between the expected and actual behavior. This visual representation is invaluable in understanding the data flow and spotting anomalies. For instance, if a register is not being written to as expected, a waveform viewer can pinpoint the exact cycle where the problem originates.

If the failure is intermittent, I might need to increase the simulation’s logging verbosity or add assertions to critical points to better understand the conditions under which the failure occurs. Sometimes, recreating the failure involves carefully crafting specific test cases, using constrained-random verification techniques to explore the design’s behavior under various scenarios. Finally, documenting the bug fix, including a detailed description of the issue, its root cause, and the implemented solution, is crucial for preventing similar issues in the future.

Q 9. What is your experience with constrained random verification?

Constrained random verification (CRV) is a powerful technique I frequently employ to improve verification efficiency. It involves generating test cases randomly, but within predefined constraints. Imagine it like shuffling a deck of cards, but only allowing certain combinations, thus focusing the test on specific areas of interest.

My experience includes using CRV extensively in various projects, often combined with coverage-driven verification. I’m proficient in defining constraints using SystemVerilog’s random variables and constraints, ensuring that the generated tests explore the design space thoroughly. For example, I might constrain the data width and address ranges to limit the number of tests, while still exploring a significant portion of the design’s functionality. I also have experience using advanced techniques like weight constraints to prioritize the generation of certain test cases over others.

One notable project involved verifying a complex DMA controller. Using CRV, I could generate thousands of tests covering different data transfers, burst sizes, and memory addresses, drastically reducing verification time compared to manually creating testbenches.

Q 10. Explain your understanding of functional coverage.

Functional coverage measures how thoroughly a verification plan has exercised the design’s functionality. It’s akin to a checklist ensuring that all the key features have been tested. High functional coverage provides confidence that the design behaves correctly across its intended operating range.

I use functional coverage extensively, typically defining coverage points in SystemVerilog using the covergroup construct. These coverage points represent specific features or aspects of the design’s functionality, such as specific register values, control signal sequences, or data path operations. Each coverage point contains bins, which represent the different possible values or states.

For example, in verifying a processor, I might define a coverage group to track the coverage of different instruction types (add, subtract, branch, etc.). Each instruction type would be a bin. As the simulation runs, the testbench collects coverage data and reports on the percentage of bins hit. This helps in identifying areas of the design that haven’t been adequately tested, allowing us to develop additional test cases to improve coverage and build confidence in the design’s correctness.

Q 11. How do you manage verification risks and challenges?

Managing verification risks and challenges is crucial for delivering high-quality, reliable designs. My approach involves proactively identifying potential risks early in the project lifecycle and implementing mitigation strategies. This includes thoroughly understanding the design specification, identifying potential failure modes, and creating a comprehensive verification plan.

Risk management involves several steps: First, thorough requirements analysis helps pinpoint areas of potential complexity or ambiguity. Secondly, developing a clear verification plan defines the scope, methodology, and metrics (e.g., functional coverage goals). Third, regular progress monitoring tracks coverage metrics, bug fixes, and schedule adherence. Finally, code reviews and independent verification provide extra layers of quality control.

For example, if a design has a complex timing constraint, we might allocate more time for verification and include formal verification methods to check for timing-related errors. Similarly, if a design component is highly critical, we might enhance the verification plan with more rigorous testing and higher coverage goals.

Q 12. Describe your experience with formal verification techniques.

Formal verification techniques are a valuable addition to my verification toolbox. Unlike simulation, which tests a design through random or directed stimuli, formal verification mathematically proves or disproves properties of the design. This approach is especially effective in detecting corner-case errors and ensuring the absence of specific bugs, particularly for safety-critical applications.

My experience encompasses using formal verification tools to prove properties such as data consistency, deadlock freedom, and compliance with design specifications. I’m familiar with property specification languages like SystemVerilog Assertions (SVA) and their application in formal verification flows. For instance, I’ve used formal verification to prove that a complex state machine adheres to its specification by creating assertions that define the expected behavior. The formal tool then verifies if the design’s implementation satisfies these assertions.

Formal verification is particularly powerful when dealing with complex protocols or algorithms where exhaustive simulation might not be feasible. It complements simulation-based verification, providing a higher level of assurance regarding the design’s correctness.

Q 13. How do you choose the appropriate verification methodology for a given project?

Choosing the right verification methodology depends on many factors, including project goals, design complexity, risk tolerance, and available resources. It’s a balancing act between thoroughness and efficiency.

For simple designs, directed testing might suffice. However, for more complex designs, a combination of constrained random verification, coverage-driven verification, and potentially formal verification is often necessary. Factors to consider include the criticality of the design (higher criticality calls for more rigorous methods), the schedule constraints (formal verification can be more time-consuming), and the expertise of the team (choosing a methodology the team is comfortable with is crucial).

For example, a small, low-risk project might use a mostly directed approach, while a large, safety-critical project will require a more comprehensive strategy, potentially using formal methods to verify critical properties. The selection process involves carefully evaluating these trade-offs and selecting a methodology that effectively balances risk mitigation with time and resource constraints.

Q 14. What are your experience with simulation tools (e.g., ModelSim, VCS)?

I have extensive experience with industry-standard simulation tools such as ModelSim and VCS. I’m proficient in using them for both simulation and debugging purposes. My expertise extends beyond basic simulation; I’m adept at leveraging their advanced features, such as waveform analysis, code coverage analysis, and debugging tools.

For example, in ModelSim, I’m familiar with using its debugging capabilities to step through the code, inspect variables, and analyze signal values. In VCS, I leverage its powerful command-line interface for efficient batch simulation and its advanced debugging features for complex scenarios.

Beyond using these tools individually, I understand how to integrate them into a larger verification environment, incorporating them with scripting languages such as Tcl or Python to automate the verification process and generate comprehensive reports. This automation greatly improves verification efficiency and reproducibility.

Q 15. Explain your approach to test planning and execution.

My approach to test planning and execution is highly structured and iterative. It begins with a thorough understanding of the component’s specifications and requirements. I then break down the verification task into smaller, manageable units, focusing on specific functionalities and behaviors. This allows for targeted testing and easier debugging.

The planning phase involves identifying various test cases, including positive and negative tests, boundary condition tests, and stress tests. I utilize a risk-based approach, prioritizing tests that cover critical functionalities and areas with higher failure probabilities. Test cases are documented meticulously, including expected results and test data. This documentation ensures traceability and simplifies maintenance.

Execution follows a structured plan, using a combination of automated and manual tests. Automation is prioritized for repetitive tasks, ensuring consistency and efficiency. Progress is tracked closely, and any deviations from the plan are documented and addressed promptly. Regular reviews and status updates are vital to maintain transparency and facilitate timely course correction. Post-execution analysis is crucial to evaluate test effectiveness, identify gaps, and refine the verification process for future iterations.

For example, during the verification of a complex state machine, I would first identify all possible states and transitions. Test cases would be designed to cover each transition, including valid and invalid inputs. Automated scripts would be used for repetitive tests, while manual inspection would be used for complex scenarios that require human judgment.

Career Expert Tips:

- Ace those interviews! Prepare effectively by reviewing the Top 50 Most Common Interview Questions on ResumeGemini.

- Navigate your job search with confidence! Explore a wide range of Career Tips on ResumeGemini. Learn about common challenges and recommendations to overcome them.

- Craft the perfect resume! Master the Art of Resume Writing with ResumeGemini’s guide. Showcase your unique qualifications and achievements effectively.

- Don’t miss out on holiday savings! Build your dream resume with ResumeGemini’s ATS optimized templates.

Q 16. How do you ensure the quality and reliability of your verification process?

Ensuring the quality and reliability of the verification process is paramount. I achieve this through a multi-pronged strategy that emphasizes thorough planning, rigorous execution, and continuous improvement.

Firstly, a robust test plan, as described earlier, is the foundation. This includes clear test objectives, well-defined test cases, and a well-documented execution procedure. Secondly, I leverage code coverage analysis to identify untested parts of the code, ensuring comprehensive testing. Thirdly, peer reviews of test plans and code are essential for early defect detection.

Continuous integration and continuous testing (CI/CD) pipelines help automate the verification process, reducing human error and improving speed. Static analysis tools are employed to detect potential issues in the code before execution, significantly reducing debugging time. Finally, regular audits and reviews of the process itself allow for ongoing improvement based on lessons learned and emerging best practices.

For example, if code coverage analysis reveals low coverage for a particular code section, additional test cases are developed to specifically target this area, improving the overall quality of the verification.

Q 17. What are your experiences with different verification languages (e.g., SystemVerilog, Vera)?

I have extensive experience with various Hardware Verification Languages (HVLs), including SystemVerilog and Vera. SystemVerilog is my preferred choice due to its widespread adoption, rich feature set, and strong industry support. Its advanced features like Object-Oriented Programming (OOP), constrained random verification, and assertion-based verification significantly enhance productivity and test effectiveness. I am comfortable using its various components including classes, interfaces, and randomisation features for creating comprehensive testbenches.

// Example of SystemVerilog constrained random verification class transaction; rand bit [7:0] data; rand int address; constraint addr_range { address inside {[0:255]}; } endclass

My experience with Vera is primarily focused on legacy projects. While Vera offers strong capabilities for constrained random verification, SystemVerilog’s broader industry acceptance and more advanced features have led to its increased preference in recent years. I can still effectively utilize both languages when needed, depending on the project requirements and legacy codebases. My focus is always on selecting the tool best suited for the task at hand, maximizing efficiency and effectiveness.

Q 18. How do you handle conflicting requirements during verification?

Conflicting requirements are a common challenge in component verification. My approach involves a systematic process to identify, analyze, and resolve such conflicts effectively.

The first step is to meticulously document all requirements, identifying any potential areas of conflict. This often involves collaboration with stakeholders, including designers, architects, and other verification engineers. The identified conflicts are then prioritized based on their severity and potential impact on the system. A formal process of conflict resolution is followed, which may involve trade-off analysis, negotiation, or arbitration.

In some cases, it may be necessary to revisit and refine the original requirements. This process often involves discussions with the design team to clarify ambiguities or inconsistencies. Once a resolution is reached, the updated requirements are documented, and the verification plan is updated accordingly. This ensures that the verification effort targets the correct and consistent set of requirements.

For example, if a requirement for high performance conflicts with a requirement for low power consumption, a trade-off analysis would be performed to find the optimal balance between the two, often documented as a design decision.

Q 19. Explain your understanding of code coverage analysis and its importance.

Code coverage analysis is a crucial technique in component verification that measures the extent to which the code has been exercised by the test suite. It’s a vital tool for assessing the completeness and effectiveness of the verification process.

Several types of code coverage exist, including statement coverage (measuring the percentage of statements executed), branch coverage (measuring the percentage of branches taken), and path coverage (measuring the percentage of all possible paths executed). Each type provides different levels of granularity and insight. Higher coverage generally indicates more thorough testing; however, high coverage alone doesn’t guarantee the absence of bugs, as it is possible to have high coverage and still miss critical defects.

Code coverage analysis helps identify gaps in testing. If a significant portion of code remains untested, it highlights areas that require additional attention. This process ensures that the verification effort is comprehensive and aims for high-quality verification.

The use of code coverage tools and metrics improves test planning and execution by providing a quantifiable measure of testing completeness. This allows for targeted improvements, ensuring that high-risk areas are thoroughly tested.

Q 20. What are some common challenges you face in component verification?

Component verification presents several common challenges. One significant challenge is the complexity of modern designs. The increasing size and complexity of designs makes comprehensive testing a significant undertaking. This complexity necessitates advanced techniques and tools to manage the verification effort efficiently. Another challenge is the ever-shrinking time-to-market pressure. Verification efforts must be optimized to meet tight deadlines without compromising quality.

Dealing with ambiguous or incomplete requirements is also a frequent challenge. Without clear and precise specifications, creating effective test cases becomes significantly more difficult. Similarly, ensuring adequate test coverage can be problematic. It’s often difficult to achieve 100% coverage, especially for complex components, demanding intelligent test planning and efficient strategies.

Finally, debugging failures can be complex and time-consuming. Identifying the root cause of failures in complex designs requires effective debugging tools and techniques. A structured approach to debugging and proper documentation are essential to address these challenges efficiently.

Q 21. Describe your experience with static and dynamic verification techniques.

Static and dynamic verification techniques are complementary approaches to ensuring component quality. Static verification involves analyzing the design or code without actually executing it. This approach primarily focuses on finding structural problems and potential defects early in the design process. Common static verification techniques include code review, lint checks, and formal verification.

Dynamic verification, on the other hand, involves executing the design or code and observing its behavior. This allows for validating functional behavior and identifying runtime errors. Techniques like simulation, emulation, and hardware acceleration are used in dynamic verification. Dynamic verification is critical for validating the behavior under various operating conditions and verifying timing and performance aspects.

I employ both static and dynamic techniques in a complementary fashion throughout the verification process. Static techniques identify potential problems early, reducing the burden on dynamic verification. Dynamic verification validates the behavior, confirming that the design works correctly as intended. A combination of these techniques provides a more robust and thorough verification process, significantly improving the quality and reliability of the resulting component.

Q 22. How do you measure the effectiveness of your verification efforts?

Measuring the effectiveness of verification efforts isn’t simply about achieving 100% code coverage. It’s about assessing whether we’ve sufficiently demonstrated the component’s functionality and robustness to meet its specifications and handle anticipated real-world scenarios. We use a multi-faceted approach:

Functional Coverage: This measures how thoroughly we’ve tested the various features and functionalities of the component. We define specific coverage points based on the specification, and our verification plan aims to achieve high functional coverage (ideally, close to 100%, but the exact target depends on risk assessment). We use tools to track this, like code coverage analysis and functional coverage metrics from our simulators.

Code Coverage: While not a sole indicator, code coverage helps identify untested code paths. High code coverage (statement, branch, path) reduces the risk of undiscovered bugs. We use tools that provide detailed reports, highlighting areas needing further attention. However, we understand that 100% code coverage doesn’t guarantee 100% functional correctness.

Defect Density: Tracking the number of bugs found during verification per 1000 lines of code (KLOC) provides a metric for the effectiveness of our verification process. A lower defect density suggests a more robust and thorough verification process.

Simulation Runtime: Efficient verification requires minimizing simulation time. We track this to identify bottlenecks and optimize our testbenches. This can reveal inefficiencies in our verification methodology, like overly complex test scenarios.

Verification Closure: Ultimately, the effectiveness of our efforts is determined by achieving verification closure. This means having sufficient evidence that the component meets its specifications and is ready for integration.

By combining these metrics, we gain a comprehensive picture of our verification efforts’ effectiveness, allowing us to iteratively improve our processes.

Q 23. Explain your approach to regression testing and its benefits.

Regression testing is crucial for ensuring that new code changes or bug fixes don’t introduce unintended consequences or break existing functionality. My approach involves a combination of automated and manual tests:

Automated Regression Suite: We maintain a comprehensive suite of automated tests that cover core functionalities. These tests are run automatically whenever code changes are integrated. This quick feedback loop catches regressions early.

Targeted Regression Tests: For specific code modifications, we design targeted tests focusing on the affected areas and their interactions with other parts of the system. This ensures that the fix is effective and doesn’t create unforeseen issues.

Test Prioritization: Not all tests are created equal. We prioritize tests based on risk assessment, focusing on critical features and frequently used functionalities. This maximizes efficiency by focusing on the most impactful tests first.

Regression Test Management Tool: We utilize tools to manage and track our regression test suite, providing detailed reports and identifying trends in failures. This helps maintain the suite’s integrity and identify areas requiring further attention.

The benefits of regression testing are clear: reduced risk of introducing new bugs, improved software quality, and increased confidence in the stability of the system. It’s a fundamental part of a robust verification plan, preventing costly rework later in the development cycle.

Q 24. How do you work with design teams to integrate verification into the design process?

Integrating verification into the design process is essential for preventing costly errors downstream. My approach focuses on collaboration and early involvement:

Early Involvement: We engage with design teams from the initial stages of the design process, participating in design reviews and contributing to architectural discussions. This allows us to understand the design intent and identify potential verification challenges early on.

Concise Specifications: Well-defined specifications are paramount. We work closely with designers to ensure the specifications are clear, unambiguous, and complete, providing a solid foundation for effective verification.

Test Plan Co-creation: We collaborate on creating comprehensive verification plans that align with the design goals. This involves identifying key verification points, defining coverage metrics, and outlining the verification strategy. The plan is a living document that adapts as the design evolves.

Verification IP Integration: We work with designers to integrate Verification IPs (VIPs) seamlessly into their design flow. This ensures that the VIPs are used consistently and efficiently throughout the verification process.

Continuous Feedback Loop: We foster a continuous feedback loop with the design team, providing regular updates on verification progress and identifying potential design flaws. This collaborative approach allows for proactive problem-solving and improved design quality.

By working closely with designers, we create a unified process where verification is not an afterthought but an integral part of the development life cycle.

Q 25. What are your experiences with various verification IP (VIP) solutions?

I have extensive experience with various VIP solutions, including those from major vendors like Synopsys, Cadence, and Mentor Graphics. My experience extends across different protocols such as AMBA AXI, PCIe, Ethernet, and USB. I’ve worked with both commercially available and internally developed VIPs.

When choosing a VIP, factors such as accuracy, completeness of features, ease of integration, support, and cost are critical. I’ve found that commercially available VIPs often provide advanced features, extensive documentation, and readily available support; however, they can be more costly. Internally developed VIPs can offer more customization but require significant investment in development and maintenance.

My experience has taught me the importance of thorough evaluation before selecting a VIP solution. This includes testing the VIP against known good designs, analyzing its performance, and verifying its conformance to relevant standards. A well-chosen and properly integrated VIP is invaluable in accelerating the verification process and improving its overall effectiveness.

Q 26. Describe a time you had to troubleshoot a complex verification issue. What was your approach?

During the verification of a high-speed serial interface, we encountered a seemingly random data corruption issue. Initial investigations showed no obvious errors in the design or the testbench. My approach was systematic:

Reproducibility: First, I focused on consistently reproducing the issue. This involved carefully documenting the conditions that led to the failure. It turned out the error occurred only under specific data patterns and clock conditions.

Isolation: I systematically isolated the problem by dividing the system into smaller blocks and verifying each block independently. This pinpointed the issue to a specific section of the data path.

Simulation Debug: I used advanced debugging techniques such as waveform analysis, assertions, and coverage analysis within the simulator to understand the data flow and identify the root cause. Waveform analysis revealed a timing anomaly in the data path under certain conditions.

Code Review: A thorough code review of the suspicious sections identified a subtle timing error in the data path’s synchronization logic, introduced by a recent modification.

Fix and Retest: Once the bug was identified and corrected, I conducted rigorous regression testing to ensure the fix didn’t create new problems.

This experience highlighted the importance of methodical troubleshooting, systematic analysis, and comprehensive debugging tools in solving complex verification challenges.

Q 27. What are your strategies for improving the efficiency of your verification process?

Improving the efficiency of the verification process is an ongoing effort. My strategies include:

Constraint-Random Verification: Using constrained-random verification significantly reduces the need for manually creating test cases. This dramatically increases verification coverage while reducing effort. We leverage SystemVerilog’s powerful features to create efficient and reusable testbenches.

Functional Coverage Driven Verification: We define specific functional coverage points early in the process, driving the development of tests to meet those targets. This ensures that we focus on the most important aspects of the design and avoid wasting time on less critical areas.

Testbench Reuse and Automation: We build reusable testbench components and leverage automation to minimize repetitive tasks, such as test case generation and execution. This reduces development time and improves consistency.

Formal Verification: For critical parts of the design, formal verification techniques can provide a more comprehensive and mathematically rigorous verification approach, complementing simulation-based techniques.

Continuous Integration and Continuous Verification (CI/CV): Integrating the verification process into a CI/CV pipeline enables quicker feedback and reduces overall verification time.

Continuous improvement is key. We regularly review our processes, identify bottlenecks, and implement improvements to optimize efficiency.

Q 28. How do you stay current with the latest advances in component verification techniques?

Staying current in the rapidly evolving field of component verification requires a multifaceted approach:

Industry Conferences and Workshops: Attending conferences like DVCon, DesignCon, and SNUG provides exposure to the latest techniques, tools, and methodologies. These events offer opportunities to network with other experts and learn from best practices.

Technical Publications and Journals: Staying informed through journals like IEEE Transactions on Computer-Aided Design and relevant industry publications helps keep abreast of the latest research and advancements.

Online Courses and Training: Online platforms offer various courses and training programs covering advanced verification techniques and tools. This allows for continuous learning and skill enhancement.

Professional Networking: Engaging with the verification community through online forums, professional organizations, and collaborations keeps me informed about emerging trends and challenges.

Hands-on Experience: The most effective way to stay current is through hands-on experience with new technologies and tools. This includes experimenting with new verification methodologies and applying them to real-world projects.

By actively participating in these activities, I ensure my expertise remains up-to-date, enabling me to contribute effectively to the advancement of component verification.

Key Topics to Learn for Component Verification Interview

- Verification Methodologies: Understand and compare different verification approaches like simulation, emulation, formal verification, and hardware-assisted verification. Consider their strengths and weaknesses in various contexts.

- Testbench Development: Master the design and implementation of effective testbenches, including stimulus generation, response checking, and coverage analysis. Focus on techniques for efficient and reusable testbench architectures.

- Assertion-Based Verification (ABV): Learn how to write and utilize assertions to formally specify and verify the functionality of components. Understand the benefits of ABV and how it improves verification efficiency.

- Coverage Metrics and Closure: Grasp the importance of code coverage, functional coverage, and assertion coverage in achieving verification closure. Know how to analyze coverage reports and identify gaps in verification.

- Verification Languages (SystemVerilog, UVM): Demonstrate proficiency in at least one industry-standard verification language. Focus on object-oriented programming concepts within the context of verification.

- Debugging and Troubleshooting: Develop skills in identifying and resolving verification issues. Practice debugging techniques for both simulation and hardware environments.

- Constraint Randomization: Learn how to effectively use constraint random verification to generate diverse test cases and improve the efficiency of your verification process.

- Practical Application: Be prepared to discuss real-world examples of component verification projects, highlighting your contributions and problem-solving approaches.

Next Steps

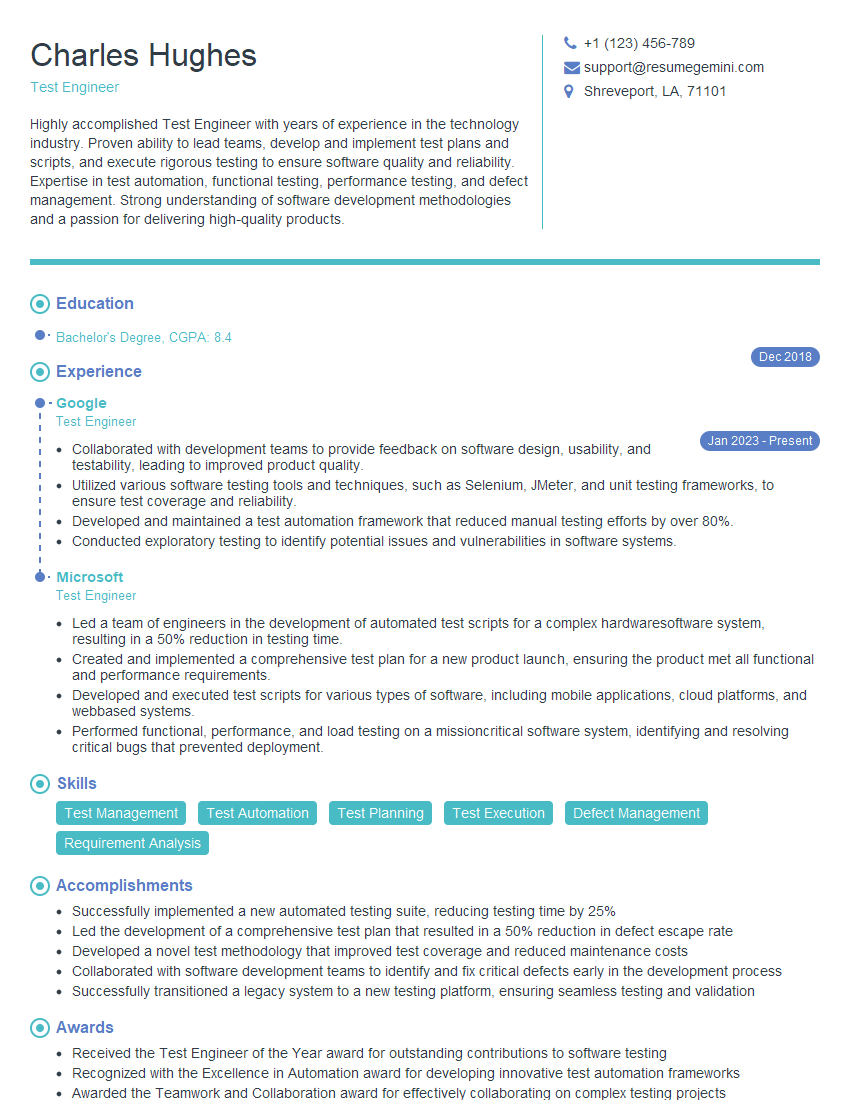

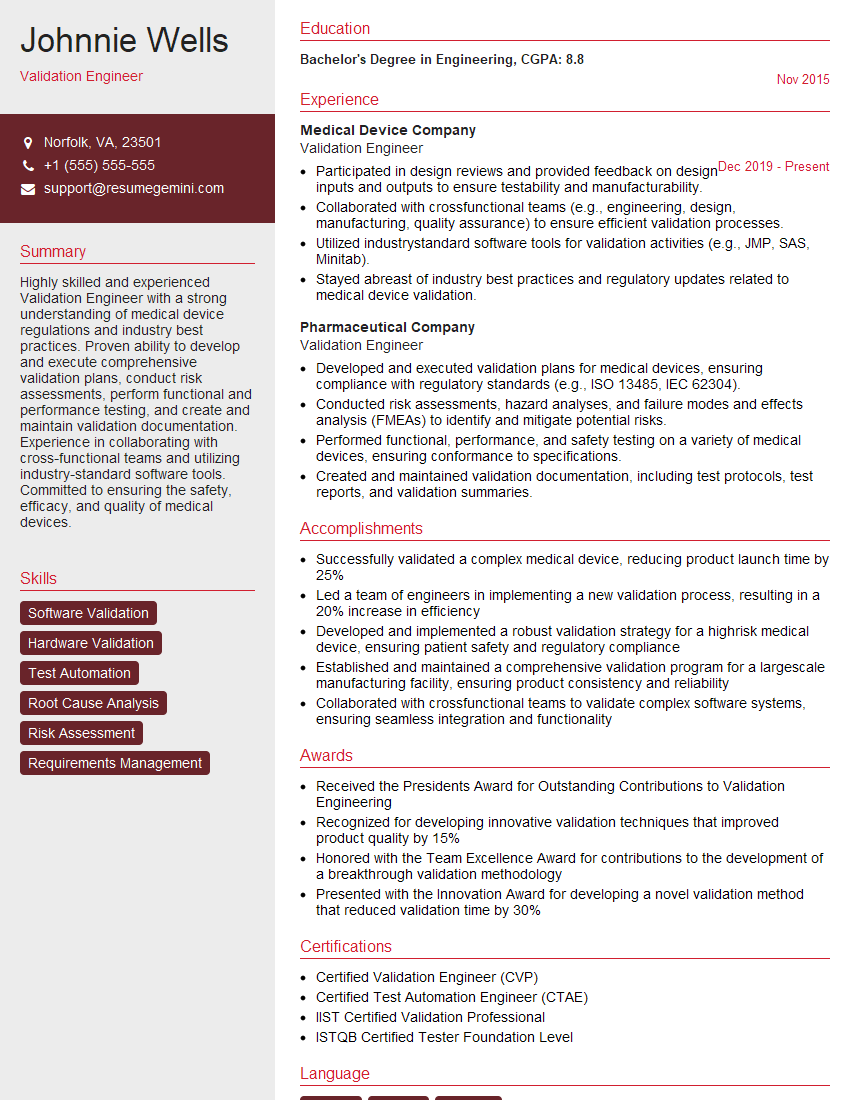

Mastering Component Verification is crucial for career advancement in the semiconductor and electronics industries. It opens doors to highly sought-after roles with excellent growth potential. To maximize your job prospects, it’s essential to create a compelling and ATS-friendly resume that showcases your skills and experience effectively. ResumeGemini is a trusted resource to help you build a professional resume that stands out. They offer examples of resumes tailored to Component Verification to help guide you in creating yours, ensuring your qualifications are clearly presented to potential employers.

Explore more articles

Users Rating of Our Blogs

Share Your Experience

We value your feedback! Please rate our content and share your thoughts (optional).

What Readers Say About Our Blog

Hello,

we currently offer a complimentary backlink and URL indexing test for search engine optimization professionals.

You can get complimentary indexing credits to test how link discovery works in practice.

No credit card is required and there is no recurring fee.

You can find details here:

https://wikipedia-backlinks.com/indexing/

Regards

NICE RESPONSE TO Q & A

hi

The aim of this message is regarding an unclaimed deposit of a deceased nationale that bears the same name as you. You are not relate to him as there are millions of people answering the names across around the world. But i will use my position to influence the release of the deposit to you for our mutual benefit.

Respond for full details and how to claim the deposit. This is 100% risk free. Send hello to my email id: [email protected]

Luka Chachibaialuka

Hey interviewgemini.com, just wanted to follow up on my last email.

We just launched Call the Monster, an parenting app that lets you summon friendly ‘monsters’ kids actually listen to.

We’re also running a giveaway for everyone who downloads the app. Since it’s brand new, there aren’t many users yet, which means you’ve got a much better chance of winning some great prizes.

You can check it out here: https://bit.ly/callamonsterapp

Or follow us on Instagram: https://www.instagram.com/callamonsterapp

Thanks,

Ryan

CEO – Call the Monster App

Hey interviewgemini.com, I saw your website and love your approach.

I just want this to look like spam email, but want to share something important to you. We just launched Call the Monster, a parenting app that lets you summon friendly ‘monsters’ kids actually listen to.

Parents are loving it for calming chaos before bedtime. Thought you might want to try it: https://bit.ly/callamonsterapp or just follow our fun monster lore on Instagram: https://www.instagram.com/callamonsterapp

Thanks,

Ryan

CEO – Call A Monster APP

To the interviewgemini.com Owner.

Dear interviewgemini.com Webmaster!

Hi interviewgemini.com Webmaster!

Dear interviewgemini.com Webmaster!

excellent

Hello,

We found issues with your domain’s email setup that may be sending your messages to spam or blocking them completely. InboxShield Mini shows you how to fix it in minutes — no tech skills required.

Scan your domain now for details: https://inboxshield-mini.com/

— Adam @ InboxShield Mini

Reply STOP to unsubscribe

Hi, are you owner of interviewgemini.com? What if I told you I could help you find extra time in your schedule, reconnect with leads you didn’t even realize you missed, and bring in more “I want to work with you” conversations, without increasing your ad spend or hiring a full-time employee?

All with a flexible, budget-friendly service that could easily pay for itself. Sounds good?

Would it be nice to jump on a quick 10-minute call so I can show you exactly how we make this work?

Best,

Hapei

Marketing Director

Hey, I know you’re the owner of interviewgemini.com. I’ll be quick.

Fundraising for your business is tough and time-consuming. We make it easier by guaranteeing two private investor meetings each month, for six months. No demos, no pitch events – just direct introductions to active investors matched to your startup.

If youR17;re raising, this could help you build real momentum. Want me to send more info?

Hi, I represent an SEO company that specialises in getting you AI citations and higher rankings on Google. I’d like to offer you a 100% free SEO audit for your website. Would you be interested?

Hi, I represent an SEO company that specialises in getting you AI citations and higher rankings on Google. I’d like to offer you a 100% free SEO audit for your website. Would you be interested?

good