Feeling uncertain about what to expect in your upcoming interview? We’ve got you covered! This blog highlights the most important FPGA and Microcontroller Programming interview questions and provides actionable advice to help you stand out as the ideal candidate. Let’s pave the way for your success.

Questions Asked in FPGA and Microcontroller Programming Interview

Q 1. Explain the difference between a combinational and sequential circuit.

The fundamental difference between combinational and sequential circuits lies in their dependence on time. A combinational circuit’s output depends solely on its current inputs; there’s no memory of past inputs. Think of a simple logic gate like an AND gate: the output is HIGH only when both inputs are HIGH. The output changes instantaneously with any change in input.

In contrast, a sequential circuit’s output depends not only on the current inputs but also on its past inputs (its state). This ‘memory’ is crucial. Flip-flops, registers, and counters are all examples of sequential circuits. Imagine a counter: its output (the count) changes sequentially based on clock pulses and previous states. The current count is a function of both the current clock pulse and the previous count.

Analogy: Think of a calculator. Adding two numbers (combinational) immediately gives the result. But if you’re using the calculator’s memory function to store numbers for a more complex calculation (sequential), the output depends on previous operations as well.

- Combinational: Immediate output based on current input. Examples: Adders, multipliers, encoders, decoders.

- Sequential: Output depends on current input and past states. Examples: Counters, registers, shift registers, Finite State Machines (FSMs).

Q 2. Describe the various types of memory available in FPGAs.

FPGAs utilize various types of memory, each optimized for different tasks. The key types include:

- Block RAM (BRAM): This is the workhorse for larger memory blocks. BRAMs are dual-ported (meaning they can be read from and written to simultaneously) and offer high bandwidth, making them ideal for storing large data sets or implementing buffers. Consider implementing a video frame buffer; BRAM is the perfect choice.

- Distributed RAM (Distributed RAM): Smaller, faster memory elements scattered throughout the FPGA fabric. They are convenient for implementing small lookup tables or caches, where quick access is paramount. A small state machine might utilize distributed RAM for its state register.

- Registers: The fundamental building blocks of sequential circuits. They store individual bits of data. They’re ubiquitous and essential for storing intermediate results in any FPGA design.

- Single-Port RAM (Single Port RAM): Simpler and smaller than BRAM, they’re ideal when only one access (read or write) is needed at a time. Less flexible than dual-ported memory, they save on resources if the application doesn’t require simultaneous access.

The choice of memory type depends heavily on the application’s requirements concerning speed, size, and access patterns.

Q 3. What are the advantages and disadvantages of using FPGAs over microcontrollers?

FPGAs and microcontrollers both serve as programmable logic devices, but they cater to different needs. The choice between them hinges on the application’s requirements.

FPGAs (Field-Programmable Gate Arrays):

- Advantages: High parallelism, customizable logic, high performance for specific tasks, can implement complex algorithms in hardware, excellent for high-throughput applications like signal processing.

- Disadvantages: Higher power consumption (generally), higher cost (per unit), steeper learning curve, more complex design flow, limited on-chip peripherals.

Microcontrollers:

- Advantages: Lower cost (per unit), lower power consumption, simpler design flow, rich set of on-chip peripherals (timers, ADC, UART, etc.), easier to program.

- Disadvantages: Limited parallelism, fixed architecture, performance bottlenecks for compute-intensive tasks, less flexibility in customization.

Example: A high-speed image processing application would benefit significantly from an FPGA’s parallelism, whereas a simple embedded system controlling a small motor might be better suited for a microcontroller’s low-power and cost advantages.

Q 4. Explain the concept of clock domain crossing and how to handle it.

Clock domain crossing (CDC) occurs when data is transferred between different clock domains – circuits operating with different clock frequencies or phases. This presents a significant challenge because the data might not be stable when sampled in the destination clock domain, leading to unpredictable behavior.

Handling CDC: Proper CDC handling is critical to prevent metastability. Common techniques include:

- Asynchronous FIFOs: These FIFOs handle the data transfer between clock domains using handshaking signals, ensuring data integrity. They gracefully manage the timing discrepancies between clocks.

- Multi-flop synchronizers: This involves using multiple flip-flops in the receiving clock domain to synchronize the data. The probability of metastability decreases exponentially with the number of synchronizer stages, but it never reaches zero.

- Gray codes: If data represents a state, using a Gray code minimizes the number of bits changing simultaneously during a transition, thereby reducing the risk of metastability.

The selection of the method depends on data rate, data width, and latency tolerance.

Q 5. What are metastability and how to mitigate it?

Metastability is a critical issue in digital circuits when a flip-flop’s output is undetermined after it is triggered by a signal that changes close to the clock edge. It is not a stable ‘0’ or ‘1,’ but rather a state somewhere in between. This unpredictable output can propagate through the system, causing intermittent errors.

Mitigation techniques are similar to those used to handle clock domain crossing:

- Multiple-flop synchronizers: As mentioned earlier, adding multiple flip-flops in series significantly reduces (but doesn’t eliminate) the probability of a metastable output propagating.

- Careful clocking design: Designing circuits that avoid clock skew and jitter minimizes the chances of signals arriving too close to clock edges.

- Asynchronous FIFOs: Using FIFOs to transfer data between clock domains eliminates the risk of propagating metastability.

- Proper signal filtering: Adding debouncing circuits can help prevent metastability caused by noisy or glitchy input signals.

It is important to remember that metastability can never be entirely eliminated, only its probability can be reduced to an acceptably low level.

Q 6. Explain different types of Finite State Machines (FSMs).

Finite State Machines (FSMs) are fundamental to sequential circuit design. They model systems that transition between a finite number of states based on input signals and their current state. There are two main types:

- Moore FSM: The output is solely a function of the current state. The output remains constant during a given state, changing only when the state changes. Think of a traffic light controller: the light’s color (output) depends on the traffic light’s current state (e.g., green, yellow, red).

- Mealy FSM: The output is a function of both the current state and the current input. The output can change even without a state change, depending on the input. Imagine a vending machine: the output (dispensing the item) depends on both the machine’s internal state (e.g., ready to dispense, waiting for money) and the current input (coins inserted).

Other Classifications: FSMs can also be classified based on their implementation (e.g., one-hot encoding, binary encoding) or their design style (e.g., synchronous, asynchronous).

Example (Moore FSM in VHDL):

type state_type is (IDLE, PROCESS_A, PROCESS_B); signal current_state: state_type := IDLE; signal output: std_logic; process (clk, reset) begin if reset = '1' then current_state <= IDLE; output <= '0'; elsif rising_edge(clk) then case current_state is when IDLE => -- ... some logic here current_state <= PROCESS_A; when PROCESS_A => output <= '1'; -- Output determined by state -- ... some logic here current_state <= PROCESS_B; when PROCESS_B => output <= '0'; -- Output determined by state -- ... some logic here current_state <= IDLE; when others => null; end case; end if; end process; Q 7. Describe your experience with VHDL or Verilog.

I have extensive experience with both VHDL and Verilog, having used them extensively throughout my career in FPGA development. My proficiency spans the entire design flow, from writing RTL code to synthesis, implementation, and verification.

I’m comfortable working with complex designs, including:

- Designing and implementing complex state machines using both languages.

- Utilizing various synthesis techniques to optimize resource utilization and performance.

- Writing and applying testbenches for thorough verification of designs.

- Working with different FPGA architectures (Xilinx, Altera/Intel).

- Integrating IP cores into larger projects.

- Debugging and troubleshooting designs using simulation and hardware-based debugging tools.

For instance, in a recent project involving a high-speed data acquisition system, I used VHDL to design a parallel data processing pipeline, optimizing it for throughput and minimizing latency. In another project using Verilog, I implemented a sophisticated communication protocol, integrating it seamlessly with existing IP blocks within an FPGA. I am proficient in both languages and choose the one best suited to the project’s requirements and team preferences.

Q 8. How do you debug an FPGA design?

Debugging an FPGA design is a crucial step in ensuring its functionality. It’s like finding a faulty wire in a complex circuit board – you need a systematic approach. My debugging strategy typically starts with simulation. I use tools like ModelSim or QuestaSim to verify the HDL code’s behavior before even synthesizing it to hardware. This catches many logical errors early on.

Next, I utilize the FPGA vendor’s debugging tools. For example, in Xilinx Vivado, I use Integrated Logic Analyzer (ILA) cores and Virtual I/O to monitor internal signals. Imagine these as probes strategically placed within the FPGA to observe signal values during runtime. I can then analyze waveforms to pinpoint the exact location of any anomalies.

Implementation debugging involves examining the synthesized netlist and placed/routed design. This helps identify potential timing issues or resource conflicts. Tools like Vivado’s timing report are invaluable here. I check for setup and hold violations, critically examining critical paths.

In-system debugging, when available, is my final step. Using a JTAG debugger, I can step through code, watch variables, and set breakpoints, much like debugging software. I’ve successfully used this to resolve tricky timing-related bugs.

Beyond tools, a systematic approach is key. I start with the highest-level functionality and gradually narrow down the scope, isolating potential problem areas. Effective commenting and a well-structured design also help greatly in debugging.

Q 9. What are different methods for timing closure in FPGA designs?

Timing closure in FPGA design is the process of ensuring that all timing requirements are met. It’s like ensuring all the cogs in a clock mechanism mesh perfectly, so the clock keeps accurate time. Failure to achieve timing closure results in a malfunctioning design.

Several methods are employed to achieve timing closure:

- Careful constraint definition: This includes defining clock frequencies, input/output delays, and other timing constraints. Accurate constraints are fundamental – inaccurate constraints can lead to false timing violations.

- Floorplanning and placement optimization: Strategic placement of critical components reduces wire lengths, directly impacting timing. Vivado and Quartus offer sophisticated placement algorithms, but manual intervention is sometimes required for critical paths.

- Routing optimization: Efficient routing minimizes signal delays. Techniques include using high-speed routing options and adjusting routing congestion. Tools provide reports to identify and resolve critical routing issues.

- Using pipeline registers: Introducing registers strategically along critical paths breaks them down into smaller segments, improving timing. This adds registers but gains significant speed.

- Clock tree synthesis: Optimizes the distribution of the clock signal across the FPGA to minimize skew, ensuring all parts of the design receive the clock simultaneously.

- Resynthesis and rerouting: Iteratively repeating the synthesis and routing steps, with minor design adjustments, can improve timing.

Example: In a high-speed data processing application, I once needed to achieve a 1 GHz clock frequency. After initial synthesis, I had timing violations. By carefully analyzing the timing report, I identified critical paths and strategically used pipeline registers, resulting in successful timing closure.

Q 10. Explain different types of FPGA architectures (e.g., LUT, DSP slices).

FPGA architectures are composed of various configurable logic blocks. Think of them as building blocks you use to construct your design.

- Look-Up Tables (LUTs): These are the fundamental building blocks. Each LUT implements a small logic function defined by a truth table. For example, a 4-input LUT can implement any Boolean function of four variables. Multiple LUTs are combined to create larger logic functions.

- Flip-Flops (FFs): These are used for storing data. They are often paired with LUTs to implement sequential logic circuits.

- Digital Signal Processing (DSP) slices: These are specialized blocks optimized for arithmetic operations, particularly multiplication and accumulation. They’re crucial for applications like digital filtering, FFTs, and other signal processing tasks. They are significantly faster and more efficient than implementing equivalent functions using only LUTs and FFs.

- Block RAM (BRAM): These are large, fast memory blocks within the FPGA. They’re used to implement various memory structures like FIFOs (First-In, First-Out) and other RAM types.

- Embedded processors (e.g., ARM cores): Some FPGAs integrate hard processor cores, allowing software and hardware integration for flexibility and efficient processing of complex tasks.

Architecture differences: Different FPGA vendors (Xilinx, Intel/Altera, Microsemi) have slightly different architectures, even if they use similar basic components. The number, size, and organization of these blocks vary, affecting the design’s size, performance, and power consumption. This is a key consideration when choosing an FPGA for a particular application.

Q 11. Describe your experience with various FPGA development tools (e.g., Vivado, Quartus).

I have extensive experience with both Xilinx Vivado and Intel Quartus Prime, the two dominant FPGA development tools. My experience spans the entire design flow, from HDL entry and synthesis to implementation, verification, and debugging.

Vivado: I’m proficient in using Vivado’s various features, including its powerful synthesis and implementation engines, integrated debugging tools (ILA, Virtual I/O), and advanced analysis capabilities (timing reports, power analysis). I’ve successfully used Vivado to design and implement high-speed data acquisition systems and complex control logic.

Quartus Prime: My experience with Quartus includes using its synthesis and fitting tools, signal-integrity analysis features, and ModelSim integration. I’ve used Quartus for projects involving custom peripherals and embedded systems designs.

Beyond these, I’m familiar with other aspects of FPGA design tools, including HDL simulators (ModelSim, QuestaSim), timing analysis tools, and various scripting languages like TCL for automating tasks. In one project, for example, I used TCL scripting to automate the process of generating various test vectors, significantly reducing development time.

Q 12. What are the different types of interrupts in microcontrollers?

Microcontrollers use interrupts to handle events asynchronously. Think of it like a phone call interrupting your work – the interrupt temporarily diverts the microcontroller’s attention to the urgent task.

Interrupt types vary depending on the microcontroller architecture, but some common types include:

- External interrupts: Triggered by signals from external devices, like buttons, sensors, or other peripherals. These are often edge-triggered (on rising or falling edges) or level-triggered (high or low).

- Internal interrupts: Generated by internal events within the microcontroller, like timer overflows, DMA completion, or software interrupts triggered by a specific instruction.

- Hardware interrupts: Triggered by hardware events, like serial communication interrupts or ADC completion interrupts. These are specific to hardware peripherals within the microcontroller.

- Software interrupts: Initiated programmatically using software instructions. They’re useful for task switching or exception handling.

Prioritization: Microcontrollers often have interrupt priority levels, ensuring that higher-priority interrupts are handled before lower-priority ones. This is essential for real-time applications where timely responses to critical events are crucial.

Example: In a motor control application, a timer interrupt might trigger periodic speed checks, while an external interrupt from a limit switch could immediately stop the motor to prevent damage.

Q 13. Explain how to manage memory in a microcontroller.

Memory management in microcontrollers is critical for efficient program execution and data storage. It’s like organizing a filing cabinet to easily access important documents. Improper memory management leads to program crashes, data corruption, or unexpected behavior.

Key aspects of memory management include:

- Memory allocation: Deciding where to store different parts of a program (code, data, stack) in the available memory space. This is often done using compiler directives or linker scripts.

- Stack management: The stack stores local variables and function call information. Overusing the stack can lead to stack overflow. Careful coding practices are vital to prevent this.

- Heap management: The heap is a pool of memory that can be dynamically allocated and deallocated during runtime. Libraries like malloc and free (in C) are used to manage the heap. Memory leaks can occur if allocated memory isn’t properly freed.

- Memory mapping: Understanding the microcontroller’s memory map – showing which addresses correspond to which memory regions (flash, RAM, peripherals) – is crucial for proper programming.

- Memory protection: Some microcontrollers offer mechanisms to protect certain memory regions from accidental access or modification.

Example: In an embedded system with limited memory, I once optimized memory usage by using statically allocated arrays instead of dynamically allocated ones where appropriate, minimizing heap usage and preventing potential memory leaks.

Q 14. What are real-time operating systems (RTOS) and their applications?

A Real-Time Operating System (RTOS) is a specialized operating system designed to manage tasks in a predictable and timely manner. Imagine a conductor orchestrating a symphony; the RTOS manages concurrent processes, ensuring each task executes within its specified time constraints.

Key features of an RTOS:

- Task scheduling: The RTOS manages multiple tasks concurrently, using scheduling algorithms (like round-robin or priority-based) to determine which task executes when.

- Inter-process communication (IPC): Facilitates communication and synchronization between different tasks.

- Real-time capabilities: Guarantees predictable task execution times, crucial for real-time applications.

- Resource management: Manages hardware and software resources, ensuring fair access to all tasks.

Applications: RTOSes are widely used in embedded systems where real-time constraints are critical. Examples include:

- Automotive control systems: Managing engine control, braking systems, and other safety-critical functions.

- Industrial automation: Controlling robots, assembly lines, and other industrial processes.

- Medical devices: Controlling pacemakers, ventilators, and other life-supporting equipment.

- Aerospace applications: Managing flight control, navigation, and other critical systems.

Example: In a robotic arm project, an RTOS was crucial for coordinating the simultaneous movements of multiple joints, while ensuring precise timing and avoiding collisions.

Q 15. Explain different communication protocols used in embedded systems (e.g., SPI, I2C, UART).

Embedded systems rely on various communication protocols to exchange data between different components. Let’s explore three common ones: SPI, I2C, and UART.

SPI (Serial Peripheral Interface):

SPI is a full-duplex, synchronous protocol that uses four wires: MOSI (Master Out Slave In), MISO (Master In Slave Out), SCK (Serial Clock), and SS (Slave Select). The master device controls the clock and selects which slave device to communicate with. It’s known for its speed and simplicity, making it ideal for high-speed data transfers, such as interfacing with sensors and memory devices. For instance, I’ve used SPI extensively to communicate with high-resolution ADCs and flash memory in various projects.

//Example SPI configuration (Conceptual) SPI_init(frequency, mode); //frequency in Hz, mode (e.g., SPI_MODE0) SPI_transmitReceive(dataOut, dataIn);I2C (Inter-Integrated Circuit):

I2C is a multi-master, synchronous serial protocol that uses two wires: SDA (Serial Data) and SCL (Serial Clock). Multiple devices can be connected to the same bus, each with a unique address. It’s a very versatile protocol, perfect for connecting many slower-speed peripherals like temperature sensors or real-time clocks. The lower speed compared to SPI means reduced electromagnetic interference, making it a good choice where noise is a concern. In one project, I used I2C to manage a network of sensors on a single bus, simplifying the wiring significantly.

// Example I2C configuration (Conceptual) I2C_init(frequency); I2C_write(deviceAddress, registerAddress, data); I2C_read(deviceAddress, registerAddress, data);UART (Universal Asynchronous Receiver/Transmitter):

UART is an asynchronous serial protocol using only two wires: TX (Transmit) and RX (Receive). It’s simple, relatively low speed, but very common for communication over longer distances or with external devices like computers. It’s often the preferred choice for debugging, as it’s easy to connect a terminal to monitor the output. For example, I frequently use UART to send debugging information from a microcontroller to a PC during development.

// Example UART configuration (Conceptual) UART_init(baudrate); UART_transmit(data); UART_receive(data);

The choice of protocol depends on factors like data rate, number of devices, distance, and power consumption requirements.

Career Expert Tips:

- Ace those interviews! Prepare effectively by reviewing the Top 50 Most Common Interview Questions on ResumeGemini.

- Navigate your job search with confidence! Explore a wide range of Career Tips on ResumeGemini. Learn about common challenges and recommendations to overcome them.

- Craft the perfect resume! Master the Art of Resume Writing with ResumeGemini’s guide. Showcase your unique qualifications and achievements effectively.

- Don’t miss out on holiday savings! Build your dream resume with ResumeGemini’s ATS optimized templates.

Q 16. How do you handle power management in microcontroller designs?

Power management is critical in embedded systems, especially in battery-powered applications. Effective power management involves minimizing current consumption without compromising functionality. Strategies include:

Clock Gating:

Disabling clocks to peripherals when not in use. For instance, if an ADC is only needed for a short period, its clock can be switched off during idle times, significantly reducing power draw.

Low-Power Modes:

Microcontrollers offer different sleep modes with varying levels of power consumption. These modes can be strategically used based on the application’s requirements. For example, a device might enter a deep sleep mode during periods of inactivity and wake up periodically to perform a specific task.

Power-Down of Peripherals:

Individually powering down peripherals that are not actively needed helps to reduce overall power consumption. This is often controllable via software registers or power management units (PMUs).

Voltage Scaling:

In some architectures, the core voltage can be dynamically adjusted, lowering power consumption when processing demands are low. This requires careful consideration of the impact on processing speed and stability.

Software Optimization:

Efficiently written code minimizes the number of clock cycles required for a given task. This reduces both energy consumption and execution time. Techniques like loop unrolling, function inlining, and careful use of data structures can contribute to significant improvements.

Often, a combination of these techniques is used to optimize power consumption, tailoring the strategy to the specific application and its operational profile. I’ve often used a combination of clock gating, low-power modes, and software optimization to extend the battery life of battery-operated devices I’ve designed.

Q 17. Describe your experience with different microcontroller architectures (e.g., ARM, AVR, MSP430).

My experience spans several microcontroller architectures, each with its strengths and weaknesses. Let’s examine a few:

ARM Cortex-M:

ARM Cortex-M architectures (like Cortex-M0+, M3, M4, M7) are widely used due to their high performance, low power consumption, and extensive ecosystem. Their 32-bit architecture allows for efficient processing of complex algorithms and tasks. I’ve worked extensively with Cortex-M4 processors, leveraging their floating-point units (FPU) for computationally intensive signal processing applications. The availability of many development tools and a huge community is a great benefit.

AVR:

AVR microcontrollers from Atmel (now Microchip) are known for their simplicity, ease of use, and extensive libraries. Their 8-bit architecture is well-suited for simpler applications where lower power consumption and ease of programming are prioritized. I’ve used AVRs in various small projects where cost and ease of development were key factors, such as basic sensor readings and small control systems.

MSP430:

MSP430 microcontrollers from Texas Instruments are particularly renowned for their ultra-low power capabilities, making them ideal for battery-powered applications with stringent energy budgets. Their architecture is optimized for energy efficiency, and I’ve employed them in designs demanding exceptionally long battery life, like wireless sensor nodes.

The choice of architecture depends on the project’s specific requirements. For example, I would select an ARM Cortex-M for a complex application requiring high performance, an AVR for a simpler project emphasizing ease of development, and an MSP430 for an application demanding minimal power consumption.

Q 18. Explain the concept of DMA.

DMA (Direct Memory Access) is a hardware feature that allows data transfer between memory locations or peripherals without direct CPU intervention. Imagine a waiter (CPU) constantly carrying plates (data) from the kitchen (peripheral) to the dining tables (memory). With DMA, the waiter can set up a conveyor belt (DMA) and let it automatically move the plates, freeing up the waiter to handle other tasks. This significantly increases efficiency and reduces CPU load.

DMA is particularly useful for high-speed data transfers, such as transferring data from an ADC to memory, or from memory to a display. It frees up the CPU to perform other tasks while the data transfer happens in the background. This is especially crucial in real-time applications where timely response is critical.

A typical DMA transfer involves specifying the source address, destination address, and the amount of data to be transferred. The DMA controller manages the transfer autonomously, generating interrupts when the transfer is complete. This allows for asynchronous operation, enhancing overall system responsiveness.

Q 19. What are your experiences with software development lifecycle in embedded systems?

My experience with the embedded systems software development lifecycle (SDLC) closely follows industry best practices. A typical process includes:

Requirements Analysis:

Defining the system’s functionality, performance requirements, and constraints.

System Design:

Creating an architectural design, including hardware and software components, and communication interfaces.

Software Design:

Detailed design of software modules, including data structures, algorithms, and flowcharts.

Implementation:

Coding the software modules using the chosen programming language (C/C++ are dominant).

Testing:

Thorough testing at different levels, including unit testing, integration testing, and system testing. This often involves simulating hardware components and using emulators/simulators.

Integration:

Integrating the software with the hardware components.

Deployment:

Deploying the software to the target hardware.

Maintenance:

Ongoing maintenance and updates as needed.

I typically utilize iterative development methodologies like Agile, ensuring regular feedback and adaptation throughout the process. Comprehensive documentation and version control are paramount to maintainability and collaboration. I’ve managed several projects following this SDLC, consistently delivering robust and reliable embedded systems.

Q 20. Explain the concept of pipelining in FPGA design.

Pipelining in FPGA design is a technique that improves throughput by dividing a complex operation into smaller, sequential stages. Imagine an assembly line: each stage performs a specific task on the data, passing the partially processed data to the next stage. This allows multiple operations to be processed concurrently, significantly increasing the overall speed.

In FPGA designs, pipelining is achieved by breaking down a combinational logic circuit into smaller parts, separated by registers. Each register holds the intermediate results, allowing the next stage to operate on new data while previous stages are still processing older data. This increases the clock frequency and processing speed, but adds latency (delay) as the data must pass through multiple stages.

The optimal pipeline depth (number of stages) is a trade-off between latency and throughput. A deeper pipeline increases throughput but adds latency. Careful consideration of pipeline balance and resource utilization is essential for efficient FPGA design. I’ve leveraged pipelining extensively in high-throughput signal processing applications in my FPGA projects to achieve significant speed increases.

Q 21. What are your experiences with version control systems (e.g., Git)?

Git is my primary version control system. I’m proficient in using Git for managing code, tracking changes, collaborating with team members, and resolving conflicts. My experience includes:

Branching and Merging:

Creating and managing feature branches, merging changes into the main branch, and resolving merge conflicts.

Remote Repositories:

Using remote repositories like GitHub, GitLab, or Bitbucket for code sharing and collaboration.

Pull Requests:

Using pull requests for code review and collaboration.

Version Tagging:

Creating tags to mark specific releases or milestones.

Git Workflow:

Following established branching strategies like Gitflow to manage releases and feature development in larger projects.

I believe in a robust version control process for any software project, regardless of size, and Git’s collaborative capabilities have been instrumental in many successful projects.

Q 22. Describe your experience with testing and verification methodologies.

Testing and verification in FPGA and microcontroller development is crucial for ensuring reliable and functional systems. My approach involves a multi-layered strategy, encompassing unit testing, integration testing, and system-level testing.

Unit Testing focuses on individual modules or components. For FPGAs, this might involve simulating individual blocks using tools like ModelSim or VCS, verifying their functionality in isolation before integration. For microcontrollers, unit testing involves testing individual functions or classes using frameworks like Unity or CppUTest.

Integration Testing combines tested units to verify their interactions. In FPGAs, this often involves co-simulation of different modules or using a hardware emulator to test interactions before loading onto the actual FPGA. In microcontrollers, integration tests verify that modules work correctly together, ensuring data flows as expected.

System-Level Testing assesses the entire system’s functionality. This often involves creating test benches that mimic real-world scenarios and observing the system’s response. For FPGAs, this might include testing the entire design under various input conditions. For microcontrollers, this involves testing the entire embedded system in its target environment.

Furthermore, I utilize formal verification methods for critical sections of the code, ensuring correctness through mathematical proof. I’m experienced with tools like Questa Formal for this purpose. Documentation of test plans, procedures, and results is a key part of my workflow, ensuring traceability and maintainability.

Q 23. How do you optimize FPGA code for resource utilization and performance?

Optimizing FPGA code requires a multi-pronged approach focusing on both resource utilization and performance. It’s often an iterative process, requiring profiling and analysis to identify bottlenecks.

- Algorithmic Optimization: This is the first step, focusing on improving the core algorithm’s efficiency. For example, using efficient data structures, minimizing computations, and exploiting parallelism are crucial.

- Coding Style: Writing concise and well-structured VHDL or Verilog is vital. Avoiding unnecessary logic and using efficient coding styles reduces resource consumption. For instance, using synthesized operators instead of manually implemented logic is beneficial.

- Pipeline Optimization: Pipelining allows for parallel processing of data, significantly improving throughput. This involves breaking down a large process into smaller stages, each operating concurrently.

- Resource Sharing: Techniques like resource sharing (e.g., multiplexing) can reduce the total number of resources used. However, this can introduce timing challenges that need careful consideration.

- Clock Management: Choosing the appropriate clock frequency and optimizing clock distribution is essential for performance and power efficiency.

- Tool Optimization: Utilizing the synthesis tool’s optimization capabilities is key. Careful examination of synthesis reports can help identify areas for improvement. Strategies like constraint management (timing constraints) are crucial for achieving desired performance targets.

For example, consider a filter implementation. Instead of a direct form realization, we can explore a transposed form or a state-space implementation for reduced resource requirements or higher performance.

//Example: Using efficient data structures instead of nested loopsQ 24. What is a critical path and how does it affect timing?

The critical path in an FPGA design is the longest path between two registers, determining the maximum clock frequency at which the circuit can operate reliably. It’s the sequence of logic elements that dictates the overall timing performance of the design.

Think of it as the slowest part of an assembly line; if one step takes longer than the others, the entire line’s speed is limited by that step. Similarly, the critical path determines the maximum clock speed because the data must propagate through it within a single clock cycle.

If the signal propagation delay on the critical path exceeds the clock period, the design will fail timing analysis. This leads to timing violations, causing unpredictable behavior. Identifying and optimizing the critical path is crucial for achieving the desired operating frequency. Tools like static timing analysis (STA) help to pinpoint these paths, aiding in optimization strategies. These may involve re-architecting the design, optimizing logic, or inserting pipelining stages.

Q 25. Describe your experience with debugging embedded systems using tools like JTAG.

JTAG (Joint Test Action Group) is an invaluable debugging tool for embedded systems. I have extensive experience using JTAG debuggers to analyze and resolve issues in both FPGAs and microcontrollers.

In FPGA debugging, JTAG allows for in-circuit observation of signals and internal states. This enables tracing data flow, identifying timing problems, and verifying the correctness of individual modules. Tools like the Xilinx ILA (Integrated Logic Analyzer) and the Altera SignalTap are commonly used for this purpose.

In microcontroller debugging, JTAG is essential for setting breakpoints, single-stepping through code, examining variables, and analyzing memory. I’m proficient in using debuggers like GDB and IDE-integrated debuggers. I commonly employ JTAG to track down issues in real-time operating systems (RTOS), interrupt handlers, and peripheral interactions. The ability to remotely access and modify memory is a key benefit in tracing down complex data-related bugs.

A real-world example: I once used JTAG debugging to track down a timing violation in an FPGA-based motor control system. By observing internal signals using the ILA, I identified the source of the violation and was able to adjust the design to meet timing constraints.

Q 26. How do you handle errors and exceptions in microcontroller programming?

Error handling in microcontroller programming is critical for robust and reliable system operation. My approach involves a layered strategy, encompassing checks at various levels.

- Input Validation: Thoroughly validating all inputs from external sources (sensors, user interfaces, etc.) before using them in calculations or operations helps prevent erroneous computations and unexpected behavior.

- Bounds Checking: Checking array indices, memory addresses, and numerical values against their permitted ranges prevents buffer overflows and out-of-bounds errors.

- Assertions: Using assertions (

assert()) allows you to specify conditions that must be true at specific points in the code. If an assertion fails, it indicates a problem within the program’s logic. - Exception Handling: Employing structured exception handling (try-catch blocks) allows the program to gracefully handle runtime errors without crashing. This involves anticipating potential exceptions and providing alternative handling mechanisms.

- Watchdog Timers: Implementing watchdog timers can prevent the microcontroller from getting stuck in an infinite loop or malfunctioning due to unexpected events. If the watchdog timer is not reset regularly, it triggers a reset of the system.

- Error Logging: Implementing error logging mechanisms is essential for post-mortem analysis. Logging critical errors, warnings, and other relevant information helps to track down the root cause of issues.

For example, in a motor control application, I would validate sensor readings, implementing error checks to handle cases where the readings are outside the expected range. This would prevent erroneous motor commands.

Q 27. Explain your experience with different development boards and tools.

I have worked with a wide range of development boards and tools throughout my career, including various microcontrollers from families such as ARM Cortex-M, AVR, and PIC, as well as Xilinx and Altera FPGAs.

My experience spans different development environments, including IDEs like Keil MDK, IAR Embedded Workbench, and Vivado for FPGAs. I’m familiar with various debugging tools – JTAG, logic analyzers, and oscilloscopes – and proficient with using different programming languages like C, C++, Verilog, and VHDL. I have hands-on experience with various development boards such as the STM32 Nucleo, Arduino Uno, and development kits from Xilinx and Intel.

For example, in one project I used a Xilinx Zynq-7000 SoC (System-on-Chip), leveraging both the programmable logic and the processing system (PS) for a high-performance embedded vision system. I utilized the Vivado design suite and its associated tools for FPGA development and the Xilinx SDK for the embedded software development on the ARM Cortex-A9 processor within the SoC. The proficiency across different hardware and software stacks enables efficient project execution.

Q 28. Describe a challenging project you worked on and how you overcame the obstacles.

One challenging project involved designing a high-speed data acquisition system for a scientific instrument. The challenge was to capture and process data at extremely high rates with minimal latency, while simultaneously managing limited resources on a low-power embedded system.

The initial approach faced difficulties meeting the timing requirements. I overcame this by using a multi-stage pipeline architecture within the FPGA, ensuring that data processing steps were parallelized, reducing the critical path length. Furthermore, careful optimization of the data path, including memory access patterns and efficient data structures, were crucial in reducing latency.

Another major challenge was minimizing power consumption. To address this, I carefully chose components, using low-power FPGA devices and implementing power-saving techniques in the microcontroller firmware. I also optimized the clock distribution strategy within the FPGA to reduce power dissipation.

Throughout this project, thorough testing and verification were crucial. I utilized JTAG debugging extensively, combined with system-level testing to ensure the system met all performance and power requirements. The success of this project highlighted the importance of careful planning, optimized design, and rigorous testing.

Key Topics to Learn for FPGA and Microcontroller Programming Interviews

Landing your dream FPGA and Microcontroller Programming role requires a solid understanding of both theoretical concepts and practical applications. This section highlights key areas to focus your preparation.

- FPGA Fundamentals: Digital logic design, VHDL/Verilog coding, synthesis and place & route processes, timing analysis and constraints, and common FPGA architectures (e.g., Xilinx, Altera).

- Microcontroller Architecture: Understanding CPU architecture, memory organization (RAM, ROM, Flash), peripherals (timers, UART, SPI, I2C), interrupt handling, and different microcontroller families (e.g., ARM Cortex-M, AVR).

- Embedded Systems Design: Real-time operating systems (RTOS), state machines, embedded software development methodologies (e.g., Agile), debugging techniques, and power management strategies.

- Practical Applications & Projects: Showcase your skills with projects demonstrating your understanding. Think about projects involving digital signal processing (DSP), motor control, communication protocols, or sensor interfacing.

- Problem-Solving & Design Approaches: Practice tackling design problems systematically. Develop strong skills in algorithm design, data structures, and efficient code writing. Be prepared to discuss your approach and trade-offs involved in different design choices.

- Testing and Verification: Master different testing methodologies for both hardware and software components. Understanding simulation, emulation, and hardware-in-the-loop (HIL) testing is crucial.

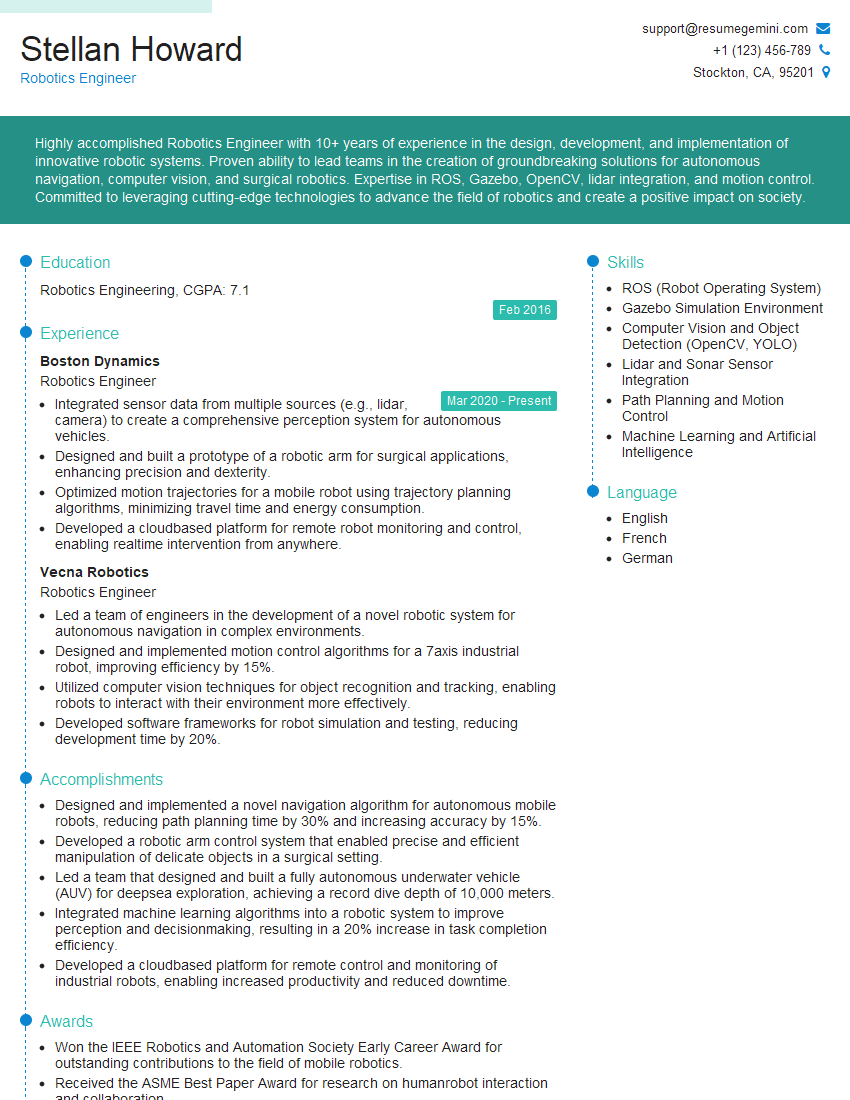

Next Steps

Mastering FPGA and Microcontroller Programming opens doors to exciting careers in various industries, from automotive and aerospace to telecommunications and consumer electronics. To maximize your job prospects, a well-crafted resume is essential. An ATS-friendly resume ensures your qualifications are effectively communicated to hiring managers and Applicant Tracking Systems (ATS). We strongly encourage you to leverage ResumeGemini, a trusted resource, to build a professional and impactful resume that highlights your skills and experience effectively. ResumeGemini provides examples of resumes tailored to FPGA and Microcontroller Programming roles, ensuring your application stands out from the competition. Take the next step and create a resume that reflects your expertise and secures your dream job.

Explore more articles

Users Rating of Our Blogs

Share Your Experience

We value your feedback! Please rate our content and share your thoughts (optional).

What Readers Say About Our Blog

Hello,

we currently offer a complimentary backlink and URL indexing test for search engine optimization professionals.

You can get complimentary indexing credits to test how link discovery works in practice.

No credit card is required and there is no recurring fee.

You can find details here:

https://wikipedia-backlinks.com/indexing/

Regards

NICE RESPONSE TO Q & A

hi

The aim of this message is regarding an unclaimed deposit of a deceased nationale that bears the same name as you. You are not relate to him as there are millions of people answering the names across around the world. But i will use my position to influence the release of the deposit to you for our mutual benefit.

Respond for full details and how to claim the deposit. This is 100% risk free. Send hello to my email id: [email protected]

Luka Chachibaialuka

Hey interviewgemini.com, just wanted to follow up on my last email.

We just launched Call the Monster, an parenting app that lets you summon friendly ‘monsters’ kids actually listen to.

We’re also running a giveaway for everyone who downloads the app. Since it’s brand new, there aren’t many users yet, which means you’ve got a much better chance of winning some great prizes.

You can check it out here: https://bit.ly/callamonsterapp

Or follow us on Instagram: https://www.instagram.com/callamonsterapp

Thanks,

Ryan

CEO – Call the Monster App

Hey interviewgemini.com, I saw your website and love your approach.

I just want this to look like spam email, but want to share something important to you. We just launched Call the Monster, a parenting app that lets you summon friendly ‘monsters’ kids actually listen to.

Parents are loving it for calming chaos before bedtime. Thought you might want to try it: https://bit.ly/callamonsterapp or just follow our fun monster lore on Instagram: https://www.instagram.com/callamonsterapp

Thanks,

Ryan

CEO – Call A Monster APP

To the interviewgemini.com Owner.

Dear interviewgemini.com Webmaster!

Hi interviewgemini.com Webmaster!

Dear interviewgemini.com Webmaster!

excellent

Hello,

We found issues with your domain’s email setup that may be sending your messages to spam or blocking them completely. InboxShield Mini shows you how to fix it in minutes — no tech skills required.

Scan your domain now for details: https://inboxshield-mini.com/

— Adam @ InboxShield Mini

Reply STOP to unsubscribe

Hi, are you owner of interviewgemini.com? What if I told you I could help you find extra time in your schedule, reconnect with leads you didn’t even realize you missed, and bring in more “I want to work with you” conversations, without increasing your ad spend or hiring a full-time employee?

All with a flexible, budget-friendly service that could easily pay for itself. Sounds good?

Would it be nice to jump on a quick 10-minute call so I can show you exactly how we make this work?

Best,

Hapei

Marketing Director

Hey, I know you’re the owner of interviewgemini.com. I’ll be quick.

Fundraising for your business is tough and time-consuming. We make it easier by guaranteeing two private investor meetings each month, for six months. No demos, no pitch events – just direct introductions to active investors matched to your startup.

If youR17;re raising, this could help you build real momentum. Want me to send more info?

Hi, I represent an SEO company that specialises in getting you AI citations and higher rankings on Google. I’d like to offer you a 100% free SEO audit for your website. Would you be interested?

Hi, I represent an SEO company that specialises in getting you AI citations and higher rankings on Google. I’d like to offer you a 100% free SEO audit for your website. Would you be interested?

good