Interviews are opportunities to demonstrate your expertise, and this guide is here to help you shine. Explore the essential Custom IC Design interview questions that employers frequently ask, paired with strategies for crafting responses that set you apart from the competition.

Questions Asked in Custom IC Design Interview

Q 1. Explain the trade-offs between CMOS and BiCMOS technologies.

CMOS (Complementary Metal-Oxide-Semiconductor) and BiCMOS (Bipolar CMOS) are two dominant technologies in integrated circuit design, each with its strengths and weaknesses. The choice depends heavily on the application’s specific requirements.

CMOS excels in its low power consumption, high integration density, and scalability. Transistors are built using MOSFETs (Metal-Oxide-Semiconductor Field-Effect Transistors), which are inherently energy-efficient due to their low leakage current. This makes CMOS ideal for battery-powered devices and large-scale integrated circuits. However, CMOS struggles with high-speed applications requiring high current drive capabilities. The inherent slow switching speeds of MOSFETs limit their performance in such scenarios.

BiCMOS combines the best of both worlds: the high speed and current drive capability of bipolar transistors (BJTs) and the low power consumption and high density of CMOS. BJTs offer superior performance at higher frequencies and higher current drives compared to MOSFETs. BiCMOS is thus preferred for applications needing both high speed and low power, such as high-speed memory interfaces or mixed-signal circuits. However, BiCMOS processes are more complex and expensive, leading to potentially lower integration density and higher costs compared to pure CMOS.

Trade-offs Summary:

- Power Consumption: CMOS significantly lower.

- Speed: BiCMOS significantly faster for high current applications.

- Integration Density: CMOS higher.

- Cost: CMOS generally lower.

For example, a high-speed data converter might benefit from BiCMOS to ensure fast sampling rates, while a large-scale microcontroller might leverage CMOS for its lower power and higher integration density.

Q 2. Describe your experience with different design methodologies (e.g., top-down, bottom-up).

I have extensive experience with both top-down and bottom-up design methodologies. The choice depends on the project’s complexity and available resources.

Top-down design starts with a high-level specification and progressively refines it into lower-level modules and components. This is beneficial for large, complex projects because it allows for better management and verification at each stage. We decompose a system into functional blocks, define interfaces, and then design and verify each block independently. This systematic approach minimizes integration issues and makes it easier to manage the complexity. I have used this approach extensively on projects involving complex SoC designs, where functional verification at each level is crucial.

Bottom-up design starts with creating basic building blocks, and then these blocks are assembled to form increasingly complex systems. This is often used for smaller projects or when designing reusable components. While quicker for smaller designs, it can become problematic in large projects as it can lead to integration difficulties if the individual blocks are not well-defined or compatible. I’ve applied this for creating reusable IP cores, for example, a highly optimized arithmetic logic unit (ALU) that can then be integrated into various designs.

Often, a hybrid approach is employed, combining aspects of both top-down and bottom-up design to leverage the advantages of both methods. For instance, a top-down approach might be used for the overall system architecture, while a bottom-up approach might be used for the design of certain critical components where optimized performance is paramount.

Q 3. How do you optimize power consumption in a custom IC design?

Power optimization is paramount in modern IC design. My strategies encompass several key areas:

- Architectural Optimization: Choosing the right architecture is the first step. For example, using lower-power clocking schemes, adopting power gating techniques to shut down inactive blocks, and utilizing power-efficient algorithms.

- Logic Optimization: Minimizing logic gates and employing techniques like logic synthesis optimization to reduce switching activity. This can be done using tools like Synopsys Design Compiler.

- Circuit-Level Optimization: Utilizing low-power design styles (e.g., reducing transistor sizes, using appropriate threshold voltages), and optimizing the transistor sizing for minimal power consumption without compromising performance. Tools like Cadence Virtuoso can be used for this.

- Clock Gating: Strategic insertion of clock gates to prevent unnecessary switching in inactive parts of the circuit.

- Voltage Scaling: Reducing the supply voltage can significantly lower power consumption. This needs careful consideration to avoid performance degradation.

- Power Analysis: Utilizing power analysis tools to identify and target the most power-hungry components in the design. This is done through simulation and analysis tools in EDA suites like Synopsys PrimeTime.

For example, in designing a low-power sensor node, I would prioritize power gating for the radio transceiver, which is only active during communication, and use low-power design styles throughout the sensor circuitry.

Q 4. Explain your understanding of clock domain crossing and how to handle it.

Clock domain crossing (CDC) occurs when data is transferred between different clock domains in a system. This is a significant challenge because asynchronous clocks can lead to metastability – an unpredictable state where the output signal is neither a ‘0’ nor a ‘1’ but is somewhere in between. This can lead to unpredictable behavior and system errors.

To handle CDC effectively, I employ several techniques:

- Asynchronous FIFOs (First-In, First-Out): These are widely used for reliable data transfer between asynchronous domains. They handle metastability by using synchronization stages and providing a robust mechanism for data handshaking.

- Multi-flop Synchronizers: Using multiple flip-flops in series to reduce the probability of metastability propagating further into the system. The probability of metastability decreases exponentially with each additional flip-flop.

- Gray Coding: For data with a small number of bits, using Gray code encoding ensures that only one bit changes between consecutive states, minimizing the impact of metastability.

- Careful Clock Domain Crossing Methodology: Following a strict methodology for crossing clock domains, including proper signaling and synchronization mechanisms to avoid race conditions and other timing hazards.

- Formal Verification: Using formal verification tools to prove the correctness of the CDC mechanism and ensure no metastability issues can occur.

Consider a scenario with a high-speed data acquisition system acquiring data at a high frequency and transmitting it to a slower processing unit. Asynchronous FIFOs are an ideal solution to handle the data transfer between these asynchronous clock domains reliably.

Q 5. Discuss your experience with various verification methodologies (e.g., simulation, formal verification).

Verification is crucial to ensure the functionality and reliability of a custom IC design. I am proficient in several verification methodologies:

- Simulation: I extensively use simulation-based verification using industry-standard tools like ModelSim and VCS. This involves creating testbenches and applying various stimulus to verify the design’s behavior against the specifications.

- Formal Verification: I utilize formal verification tools like Cadence Jasper and Synopsys VC Formal to prove the correctness of the design mathematically. Formal verification is particularly effective in detecting subtle design flaws that might be missed by simulation.

- Assertion-Based Verification (ABV): I incorporate assertions into the design to check specific properties during simulation and formal verification, making the verification process more comprehensive and automated.

- Coverage-Driven Verification: I use coverage metrics to ensure that all aspects of the design have been thoroughly verified. This helps to identify gaps in the verification process and guide the creation of additional test cases.

- Static Timing Analysis (STA): Essential for ensuring that the design meets timing requirements. Tools like Synopsys PrimeTime are utilized to analyze the timing behavior of the circuit and identify any timing violations.

For instance, in a complex communication protocol design, I would use simulation to verify the basic functionality and then leverage formal verification to prove the absence of deadlocks or other critical errors.

Q 6. Describe your experience with different layout tools and techniques.

My experience encompasses various layout tools and techniques, including:

- Cadence Virtuoso: A widely used tool for schematic capture, layout design, and simulation. I’m proficient in using its features for creating efficient and manufacturable layouts.

- Synopsys IC Compiler: This tool is frequently used for automated place and route, enabling high-quality layout generation for complex designs. My experience includes using it to optimize timing and power.

- Manual Layout Techniques: I am adept at performing manual layout when required for critical components, allowing for precise control over placement and routing to optimize performance and signal integrity.

- Floorplanning and Power Planning: I’ve extensive experience in creating efficient floorplans to manage signal routing and power distribution networks effectively, minimizing power loss and electromigration.

- Design Rule Checking (DRC) and Layout Versus Schematic (LVS): I regularly use these verification methods to ensure the layout adheres to the design rules of the chosen fabrication process and accurately represents the schematic.

For example, in a high-speed memory design, manual layout is often employed for critical path elements to ensure optimal performance, while automated place and route tools are used for less critical sections to expedite the design process.

Q 7. How do you handle signal integrity issues in high-speed designs?

Signal integrity is paramount in high-speed designs. Issues like reflections, crosstalk, and impedance mismatches can significantly degrade performance and even cause malfunctions.

My approach involves:

- Careful Signal Routing: Planning signal routing strategically to minimize the length of traces, avoid sharp bends, and maintain consistent impedance. This involves using controlled impedance routing techniques.

- Termination Techniques: Using appropriate termination techniques such as series termination or parallel termination to reduce reflections and improve signal quality. The choice of termination depends on the specific transmission line characteristics.

- Crosstalk Mitigation: Employing techniques like shielding, guard rings, and careful placement of sensitive signals to minimize crosstalk between adjacent traces. This involves understanding the coupling capacitance and inductance between traces.

- Impedance Matching: Ensuring consistent impedance throughout the signal path to prevent reflections. This often requires using impedance-controlled transmission lines.

- Signal Integrity Simulation: Using signal integrity simulation tools like HSPICE or ADS to model and analyze the signal behavior, identify potential issues, and verify the effectiveness of mitigation techniques.

In a high-speed serial link design, for example, careful impedance matching is crucial to prevent signal reflections that can lead to bit errors. Simulation and modeling tools help to predict and mitigate these potential issues before fabrication.

Q 8. Explain your experience with static timing analysis (STA).

Static Timing Analysis (STA) is a crucial step in digital IC design that verifies the timing constraints of a design. It ensures that all signals arrive at their destinations within the required time limits, preventing glitches and ensuring correct functionality. This is achieved by analyzing the propagation delays through various logic gates and interconnects, considering clock skew, setup and hold times, and other timing parameters.

My experience encompasses using industry-standard STA tools like Synopsys PrimeTime. I’ve used STA throughout the design flow, from initial synthesis to post-layout verification. A typical workflow would involve defining constraints (clock frequencies, input/output delays), running STA analysis, and then resolving timing violations. For example, if a timing violation is detected—say, a flip-flop’s data input arrives too late—I would investigate the critical path, potentially optimizing the design by resizing transistors, re-routing interconnects, or inserting buffers to reduce delay.

In one project, we encountered a critical path violation after placement and routing. Using PrimeTime’s analysis reports, we identified the bottleneck as a long interconnect between two blocks. By strategically placing repeaters along the path and fine-tuning the clock tree, we managed to successfully meet the timing constraints without compromising area or power.

Q 9. How do you perform noise analysis in analog circuits?

Noise analysis in analog circuits is essential to ensure proper circuit operation and avoid performance degradation. It involves identifying and quantifying various noise sources—thermal noise, shot noise, flicker noise—and their impact on the circuit’s signal integrity. Techniques involve simulating the noise sources and propagating their effects through the circuit.

I typically use simulators like Cadence Spectre to perform noise analysis. The process usually starts with creating a noise model of the circuit including all relevant components and their noise parameters. This is often aided by a thorough understanding of the transistors’ noise behavior at different operating conditions. The simulation then provides spectral density plots showing the noise power at various frequencies. Based on these plots, we assess the signal-to-noise ratio (SNR) and determine whether the noise level is acceptable. If not, we explore mitigation strategies, such as increasing the transistor size to reduce thermal noise, using noise-canceling techniques, or adjusting the circuit topology.

For instance, in designing a low-noise amplifier (LNA), we carefully chose the transistor types and sizes, optimized the biasing conditions, and employed techniques like cascoding to minimize noise contribution. This involved iterative simulations, analysis of results, and refinement of the design until the desired noise performance was achieved.

Q 10. Describe your experience with different types of memory (e.g., SRAM, DRAM).

My experience encompasses the design and integration of various memory types, primarily SRAM and DRAM. SRAM (Static Random-Access Memory) is characterized by its fast access times and simple architecture but higher area consumption compared to DRAM. DRAM (Dynamic Random-Access Memory) offers higher density but slower access speed due to the need for continuous refresh cycles.

I’ve been involved in designing SRAM arrays ranging from small, fast caches embedded within processors to larger off-chip memory modules. This includes the design of the sense amplifiers, bit lines, word lines, and the overall array structure, with meticulous attention paid to performance parameters like access time, power consumption and read/write stability. In DRAM design, my work has focused on understanding and mitigating refresh requirements and optimizing the sense amplifier design for stability in presence of leakage currents. In a project, we optimized an SRAM macro by leveraging advanced low-power techniques, significantly reducing its power consumption without sacrificing performance.

Furthermore, my expertise extends to understanding the trade-offs between different memory architectures and selecting the most appropriate technology for a specific application. For example, a high-performance processor might benefit from an on-chip SRAM cache, whereas a mobile device might prioritize DRAM for its high density and relatively lower power consumption (when idle).

Q 11. Explain your understanding of different types of analog filters.

Analog filters are fundamental to signal processing, used to select desired frequency components while rejecting others. There are numerous types, categorized based on their frequency response, topology, and implementation. Some common types include:

- Butterworth filters: Maximize flatness in the passband.

- Chebyshev filters: Allow for sharper roll-off but with ripples in the passband or stopband.

- Bessel filters: Prioritize linear phase response, preserving signal shape.

- Elliptic filters: Offer the sharpest roll-off but with ripples in both passband and stopband.

In addition to these filter types, different topologies are used for implementation such as Sallen-Key, Multiple Feedback, and State-Variable filters. The choice of filter type and topology depends on the specific requirements of the application, considering factors like passband ripple, stopband attenuation, phase linearity, and component count.

My experience includes designing various analog filters using different topologies. I’ve worked on designing a low-pass filter for a sensor interface where minimizing phase distortion was crucial. We opted for a Bessel filter implemented using a Sallen-Key topology. In another instance, for a high-bandwidth communication system, we needed a sharp cutoff; a Chebyshev filter proved optimal, though the ripple had to be carefully managed to avoid unacceptable signal distortion.

Q 12. How do you design for testability in a custom IC?

Design for Testability (DFT) is crucial to ensure the reliability and manufacturability of a custom IC. It involves incorporating specific techniques into the design to make it easier and more efficient to test after fabrication. The goal is to identify and isolate faults quickly and accurately.

Common DFT techniques include:

- Scan chains: These chains allow for serial access to flip-flops, facilitating the testing of internal circuit nodes.

- Built-in self-test (BIST): This involves adding self-testing capabilities to the chip, reducing the reliance on external test equipment.

- Boundary scan (JTAG): A standard that provides access to the chip’s I/O pins for testing purposes.

In my experience, I’ve used scan chain design extensively. This involved integrating scan flip-flops into the design and ensuring proper chain connectivity. I also worked on designing test patterns to effectively cover the various fault conditions. The choice of DFT technique depends on many factors, including the design complexity, test time, and cost constraints. We often incorporate multiple DFT techniques to optimize test coverage and efficiency.

For example, in a complex system-on-chip (SoC), we incorporated scan chains for the main logic blocks and used boundary scan to test the I/O interfaces. This combination helped ensure comprehensive fault coverage without incurring significant area overhead.

Q 13. Describe your experience with physical design and floorplanning.

Physical design and floorplanning are critical stages in IC design that determine the chip’s layout and physical implementation. Floorplanning involves the initial placement of major blocks (memories, processors, etc.), aiming to optimize area, power, and performance. Detailed placement and routing follow, precisely positioning components and connecting them with interconnects.

My experience includes using Electronic Design Automation (EDA) tools such as Cadence Innovus for physical design. Floorplanning involves considering various factors like power distribution, signal integrity, thermal management, and timing closure. We often employ automated tools for initial placement, and then manually adjust the layout to refine critical areas. Routing involves connecting all the components, employing various techniques to ensure signal integrity and minimal crosstalk. Post-layout timing analysis and signal integrity analysis are crucial to verify the design’s functionality and reliability.

In a recent project, we faced challenges in achieving timing closure due to the long interconnect lengths. By carefully optimizing the floorplan and utilizing advanced routing algorithms, we were able to improve timing, reduce power consumption, and meet the project’s specifications. Effective floorplanning and routing are essential for obtaining an efficient and functional IC that meets the performance and cost requirements.

Q 14. How do you manage design risks and uncertainties?

Managing design risks and uncertainties is crucial for successful IC development. It requires a proactive approach involving risk assessment, mitigation planning, and contingency measures. Potential risks include timing closure issues, power consumption exceeding limits, manufacturing defects, and unforeseen design bugs.

My approach involves a multi-pronged strategy:

- Early risk assessment: Identify potential risks during the initial design phases.

- Robust design practices: Employing design techniques to improve reliability and reduce sensitivity to variations.

- Design verification: Using simulations, formal verification, and other methods to ensure the design’s correctness.

- Contingency planning: Developing backup plans and alternative approaches to address potential issues.

- Regular monitoring and feedback: Tracking progress, identifying emerging issues, and implementing corrective actions.

For example, if timing closure is a major concern, we would aggressively focus on optimizing the critical path early in the design, potentially exploring alternative architectures or technologies if needed. Throughout the design process, we closely monitor progress, regularly reviewing simulation results and identifying potential problems before they become critical. Open communication and collaborative teamwork are key to effectively addressing risks and uncertainties.

Q 15. Explain your experience with different scripting languages (e.g., Perl, Tcl, Python).

Scripting languages are essential for automating tasks and enhancing efficiency in custom IC design. My experience spans several languages, each with its strengths. Perl, known for its text processing capabilities, was instrumental in parsing complex simulation results and generating reports. I used it extensively to automate the extraction of key metrics from simulation logs, saving significant time compared to manual analysis. Tcl, with its tight integration with EDA tools, was crucial for scripting complex design flows within Cadence Virtuoso and Synopsys IC Compiler. For instance, I leveraged Tcl to automate the generation of various design configurations for sensitivity analysis. Finally, Python, with its vast libraries like NumPy and SciPy, has become my go-to language for data analysis, algorithm development, and creating custom visualization tools. I used Python to develop a script that automatically generated plots to visualize power consumption across different operating conditions, facilitating rapid identification of power-hungry components.

- Perl: Used for report generation and data extraction from simulation logs.

- Tcl: Integrated into EDA tool flows for automation and design configuration.

- Python: Data analysis, algorithm development, and custom visualization.

Career Expert Tips:

- Ace those interviews! Prepare effectively by reviewing the Top 50 Most Common Interview Questions on ResumeGemini.

- Navigate your job search with confidence! Explore a wide range of Career Tips on ResumeGemini. Learn about common challenges and recommendations to overcome them.

- Craft the perfect resume! Master the Art of Resume Writing with ResumeGemini’s guide. Showcase your unique qualifications and achievements effectively.

- Don’t miss out on holiday savings! Build your dream resume with ResumeGemini’s ATS optimized templates.

Q 16. Describe your experience with EDA tools (e.g., Synopsys, Cadence).

My experience with EDA (Electronic Design Automation) tools is extensive, primarily focusing on Synopsys and Cadence suites. Within Synopsys, I’m proficient with IC Compiler for synthesis, PrimeTime for static timing analysis, and PrimePower for power analysis. I’ve used these tools to design and verify high-speed, low-power circuits, successfully optimizing for area, performance, and power. For example, using IC Compiler’s advanced optimization techniques, I reduced the critical path delay by 15% in a high-speed serializer design. With Cadence, I’m experienced with Virtuoso for schematic capture and layout, Spectre for simulation, and Innovus for implementation. I’ve leveraged Virtuoso’s powerful layout capabilities to create complex analog circuits, and Spectre’s advanced simulation features were vital for accurate performance verification. One project involved designing a low-noise amplifier using Virtuoso and Spectre, meeting stringent noise and gain specifications. I regularly utilize the scripting capabilities within these tools (Tcl) to automate tedious tasks and improve overall efficiency.

Q 17. How do you ensure the reliability of your custom IC design?

Ensuring reliability in custom IC design is paramount. My approach is multifaceted and incorporates several key strategies. First, a robust design methodology is crucial. This includes thorough specification, rigorous verification at multiple levels (functional, timing, power), and extensive simulation. For example, we perform extensive Monte Carlo simulations to assess the impact of process variations on circuit performance. Second, we use formal verification techniques to exhaustively check for design errors. This helps catch subtle bugs that might be missed by traditional simulation. Third, we leverage advanced techniques like design-for-testability (DFT) to ensure that the chip can be thoroughly tested after fabrication. Finally, post-silicon validation using physical prototypes is vital for confirming the design’s performance and reliability in real-world conditions. This process involves comparing the measured data from the fabricated chip with the simulated results to identify any discrepancies. Addressing any such inconsistencies requires a deep understanding of both the design and manufacturing process.

Q 18. Explain your understanding of process variations and their impact on design.

Process variations are inherent in semiconductor manufacturing, leading to variations in transistor parameters (e.g., threshold voltage, current drive strength) from one chip to another, even on the same wafer. These variations can significantly impact circuit performance and reliability. Understanding and mitigating these effects is crucial for robust design. We account for process variations through statistical static timing analysis (SSTA) and Monte Carlo simulations. SSTA uses process variation models (e.g., BSIM models) to analyze the worst-case and best-case timing paths, helping ensure timing closure under various conditions. Monte Carlo simulations run thousands of simulations with different process parameter variations to assess the probability of failure and identify sensitive design areas. For example, in a high-speed memory controller design, we used Monte Carlo simulations to identify variations affecting read latency, allowing us to implement compensating measures to ensure timing consistency across different chips. Corner-based simulations, targeting best-case and worst-case scenarios, further refine our understanding of process variation impacts.

Q 19. Describe your experience with different design constraints and how you handle them.

Design constraints encompass various limitations like area, power, performance, and noise specifications. Handling these requires a systematic approach. First, we meticulously define constraints based on the system-level requirements. These are then translated into specific constraints within the EDA tools. For example, setting timing constraints involves specifying clock frequencies, setup and hold times, and clock uncertainties. Power constraints might involve limits on total power consumption, leakage current, or switching power. Area constraints might be expressed as limits on the total chip area or specific module sizes. During the design process, iterative refinement is key. We use EDA tools to analyze the design against these constraints and make necessary adjustments, such as optimizing the placement and routing, using different library cells, or adjusting circuit parameters. Constraint management involves a trade-off analysis. For instance, we might need to compromise on power consumption to meet performance targets, and this requires careful negotiation and justification based on the system’s overall priorities. Violation analysis provided by the EDA tools helps guide this iterative process of constraint satisfaction.

Q 20. How do you debug a failing custom IC design?

Debugging a failing custom IC design is a systematic process involving several steps. First, it’s vital to have a well-structured verification plan, including simulations at various levels (unit, integration, system). This helps pinpoint the source of the failure more effectively. Once a failure is detected, I start with a thorough analysis of simulation results, focusing on waveforms, timing reports, and power analysis data. This often involves using debugging tools within the EDA environment to visualize signals and identify areas of concern. Next, I would check for constraint violations, and review the design for potential errors, like incorrect netlists, layout issues (short circuits, open circuits), or inappropriate component selection. If the problem persists, I may resort to more advanced techniques such as formal verification or static timing analysis to identify subtle timing or logical errors that might have been missed during simulation. Ultimately, a combination of systematic investigation, powerful EDA tools, and a strong understanding of circuit behavior are essential for effective debugging. Collaboration with other team members is often crucial as well.

Q 21. Explain your understanding of different types of analog-to-digital converters (ADCs).

Analog-to-digital converters (ADCs) are crucial components that convert analog signals into digital representations. Different types cater to specific needs, balancing speed, resolution, and power consumption. Here are some key types:

- Flash ADCs: These are high-speed converters that use a parallel comparator architecture to convert the input voltage into a digital code. They offer high speed but consume significant power and area.

- Pipeline ADCs: These ADCs break down the conversion process into several stages, each performing a partial conversion. They achieve a good balance between speed and power consumption.

- Sigma-Delta ADCs: These converters use oversampling and noise shaping techniques to achieve high resolution with relatively simple circuitry. They’re often preferred for low-power, high-resolution applications.

- Successive Approximation ADCs (SAR ADCs): These use a binary search algorithm to find the closest digital representation of the input voltage. They provide a good balance between speed, resolution, and power and are commonly used in many applications.

The choice of ADC depends heavily on the application’s requirements. For example, a high-speed data acquisition system would benefit from a flash ADC, while a low-power sensor application might prefer a Sigma-Delta ADC. Understanding the trade-offs between speed, resolution, power, and area is crucial when selecting the appropriate ADC architecture for a particular design.

Q 22. Describe your experience with different types of digital-to-analog converters (DACs).

Digital-to-Analog Converters (DACs) are crucial components in many electronic systems, transforming digital signals into their analog counterparts. My experience encompasses several types, each with its strengths and weaknesses:

- Binary-Weighted DACs: These are the simplest, using a network of resistors with values doubling for each bit. They’re easy to understand but suffer from accuracy issues due to resistor mismatch at higher resolutions.

- R-2R Ladder DACs: This architecture utilizes only two resistor values (R and 2R), leading to better matching and improved linearity compared to binary-weighted DACs. I’ve used them extensively in applications requiring moderate resolution and accuracy.

- Sigma-Delta DACs: These oversample the input signal and use a feedback loop to achieve high resolution with relatively simple components. Their noise shaping capabilities are a significant advantage, making them ideal for high-resolution audio applications. I’ve worked on designing a high-resolution audio DAC using this architecture, specifically focusing on optimizing noise shaping for improved dynamic range.

- Segmented DACs: These combine multiple smaller DACs to achieve higher resolution while managing the complexity. This is a cost-effective approach for high-resolution applications. I contributed to a project that implemented a segmented DAC for a high-speed data acquisition system.

The choice of DAC depends heavily on the specific application requirements. Factors like resolution, speed, power consumption, linearity, and cost all play a critical role in the selection process.

Q 23. How do you optimize for area, performance, and power (APP) in a custom IC design?

Optimizing for Area, Performance, and Power (APP) is the holy grail of custom IC design. It’s a balancing act, as improvements in one area often come at the expense of others. My approach involves a multi-pronged strategy:

- Architectural Optimization: Choosing the right architecture is paramount. For example, using a pipelined architecture can improve performance but might increase area and power. I’ve successfully implemented pipelining in high-speed data processing units, carefully balancing the trade-offs.

- Logic Optimization: Techniques like logic synthesis and optimization using tools like Synopsys Design Compiler are essential for reducing area and power consumption. I routinely employ various optimization strategies, including gate sizing, clock gating, and power gating.

- Low-Power Design Techniques: Employing techniques like voltage scaling, clock gating, power gating, and using low-power standard cells are crucial. I have experience implementing these techniques across various projects to significantly reduce power consumption while meeting performance goals. For instance, in a recent project, clock gating reduced power consumption by 15% without impacting performance.

- Physical Design Optimization: Careful placement and routing significantly impact performance and power. Using techniques like clock tree synthesis and optimization is vital for reducing skew and power. Proper placement of I/O cells minimizes noise and interference.

- Iteration and Analysis: Optimization is an iterative process. Post-layout simulations and analysis using tools like Calibre are crucial to identify bottlenecks and refine the design.

Think of it like building a car – you wouldn’t use a race car engine for a city commuter. Similarly, the optimal APP balance depends entirely on the specific application.

Q 24. Explain your understanding of different types of oscillators.

Oscillators are the heart of many circuits, generating periodic signals. My experience includes several types:

- LC Oscillators: These use an inductor (L) and capacitor (C) to create resonance. They’re simple but can be bulky and sensitive to component variations. I’ve used them in RF applications where high frequency stability is important.

- Crystal Oscillators: These utilize a piezoelectric crystal to achieve high frequency stability. Their stability makes them ideal for clock generation in systems requiring precise timing, such as microcontrollers. I’ve extensively used these in various projects requiring accurate clock signals.

- Ring Oscillators: These consist of an odd number of inverters connected in a ring. They’re simple but less precise in terms of frequency. They can be used in some low-power applications where accuracy is not critical.

- Relaxation Oscillators: These utilize charging and discharging of capacitors to generate a waveform. They are typically used for generating lower frequencies. I’ve employed them in some timing control circuits.

The selection of oscillator depends on the application requirements. For example, if high frequency stability is crucial (like a communication system), you might use a crystal oscillator; if a low-power, less-precise oscillator is needed for a simple timing function, a relaxation oscillator may suffice.

Q 25. Describe your experience with low-power design techniques.

Low-power design is critical for portable and battery-powered devices. My experience includes various techniques:

- Power Gating: Disabling unused portions of the circuit to reduce power consumption. I’ve successfully implemented this in several designs, achieving significant power savings.

- Clock Gating: Stopping the clock signal to inactive parts of the circuit. This technique is very effective in reducing dynamic power. I’ve used this in many projects, often in combination with power gating.

- Voltage Scaling: Reducing the supply voltage to reduce power consumption. However, this must be carefully managed to ensure functionality at lower voltages.

- Multi-threshold CMOS: Using different threshold voltages for different parts of the circuit to optimize power consumption. I’ve worked on projects that leveraged this technique to lower power consumption significantly.

- Low-Power Standard Cells: Using optimized standard cells designed specifically for low-power applications.

A successful low-power design often involves a combination of these techniques, carefully optimized for the specific application. The techniques are often used in conjunction, and proper analysis and verification are needed to ensure functionality at lower power levels.

Q 26. How do you ensure the security of your custom IC design?

Security in custom IC design is paramount, especially in applications like cryptography or secure communication. My approach involves multiple layers of protection:

- Hardware Security Modules (HSMs): Integrating specialized hardware components to secure sensitive operations. This involves careful design and verification of the HSM to ensure its integrity.

- Secure Boot Mechanisms: Implementing mechanisms to verify the integrity of the firmware and prevent unauthorized modification. I’ve worked on designs with secure boot processes, verifying firmware authenticity and preventing malicious code execution.

- Anti-tamper Measures: Incorporating features to detect and prevent physical tampering with the chip. This might involve using specialized packaging techniques or adding tamper detection circuits. I’ve designed circuits with integrated tamper detection capabilities, triggering a self-destruct mechanism upon tampering attempts.

- Layout Obfuscation: Making it difficult to reverse-engineer the chip’s functionality by employing techniques to obscure the layout and logic design. This is a crucial aspect of protecting intellectual property. I understand the trade-offs between layout obfuscation and area/performance.

- Formal Verification: Using formal methods to verify the security properties of the design, ensuring that vulnerabilities are identified and addressed before fabrication. This is vital for high-security applications.

Security is a continuous process. It’s not a one-time action, but a layered approach that requires careful consideration at every stage of the design process.

Q 27. Explain your experience with project management and teamwork in a custom IC design environment.

Custom IC design is inherently a collaborative effort. My experience working on large projects includes:

- Agile Methodologies: Utilizing Agile methodologies for efficient project management, allowing for flexibility and adaptation to changing requirements.

- Version Control: Employing version control systems such as Git for efficient code management and collaboration. This ensures that everyone is working on the most up-to-date version and tracks changes effectively.

- Team Communication: Maintaining clear and consistent communication within the team using tools like Jira or Slack. This is essential for timely problem-solving and ensuring everyone is aligned on project goals.

- Collaboration Tools: Using collaborative design tools to facilitate teamwork and knowledge sharing, enabling seamless collaboration on different aspects of the design.

- Mentorship and Knowledge Transfer: Actively mentoring junior engineers and sharing my expertise to develop a strong and capable team.

I’ve found that effective communication, clear roles, and well-defined processes are crucial for success in a collaborative custom IC design environment. I thrive in team environments and contribute to a positive and productive atmosphere.

Key Topics to Learn for Custom IC Design Interview

- Digital Design Fundamentals: Mastering logic gates, Boolean algebra, combinational and sequential logic circuits is crucial. Understand the trade-offs between different design choices in terms of speed, power, and area.

- Verilog/VHDL: Proficiency in at least one Hardware Description Language (HDL) is essential. Practice designing and simulating complex digital circuits using these languages. Understand timing analysis and simulation results.

- Synthesis and Place & Route: Gain a strong understanding of how your HDL code translates into physical layout. Familiarize yourself with the tools and processes involved in optimizing for performance and power consumption.

- Timing Analysis and Optimization: Learn to identify and resolve timing violations in your designs. Understand concepts like setup and hold times, clock skew, and various optimization techniques.

- Low-Power Design Techniques: Explore various power optimization methods, including clock gating, power gating, and voltage scaling. Understand the trade-offs involved in choosing the right technique.

- Memory Systems: Understand different memory architectures (SRAM, DRAM, Flash) and their characteristics. Be prepared to discuss memory controllers and interface designs.

- Verification Methodologies: Develop skills in formal verification and simulation-based verification. Understand testbench design and coverage analysis.

- Analog Circuit Design (if applicable): Depending on the specific role, you might need to demonstrate knowledge of basic analog circuit building blocks like op-amps, transistors, and basic amplifier designs.

- Problem-Solving and Design Trade-offs: Practice approaching design challenges systematically and understanding the trade-offs between various design choices (area, power, performance).

Next Steps

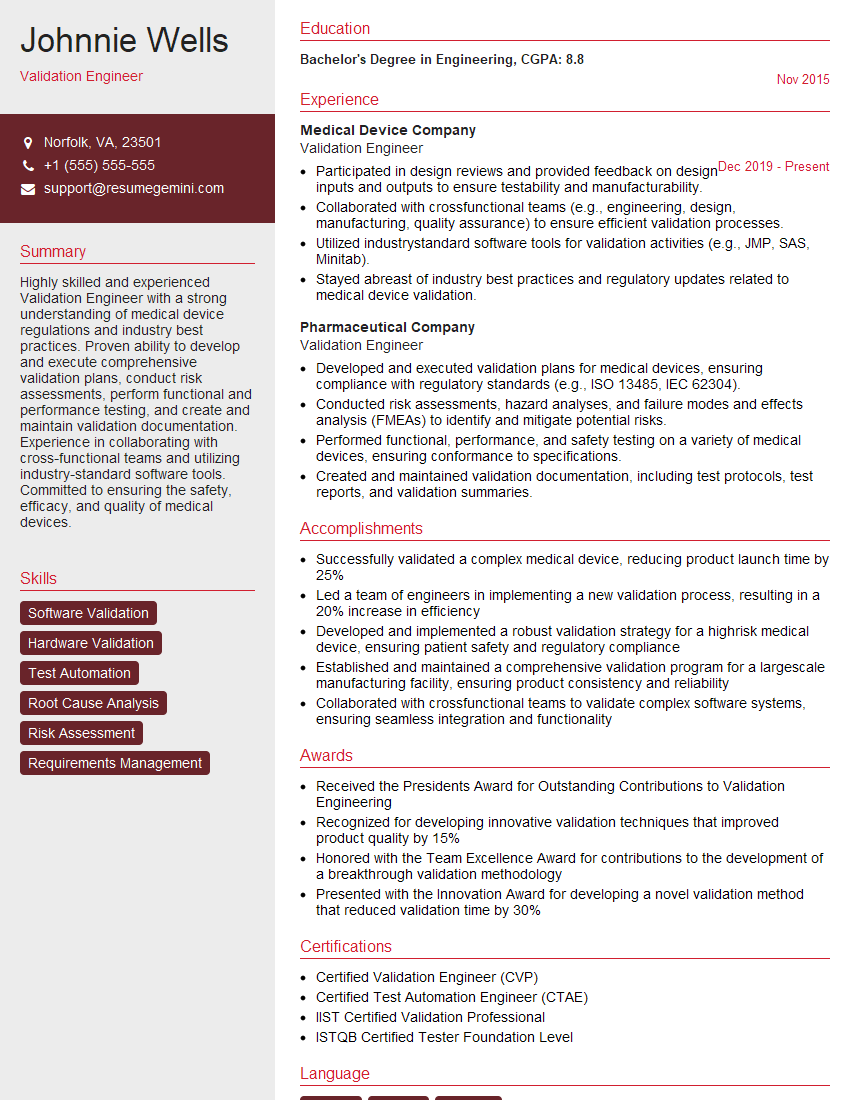

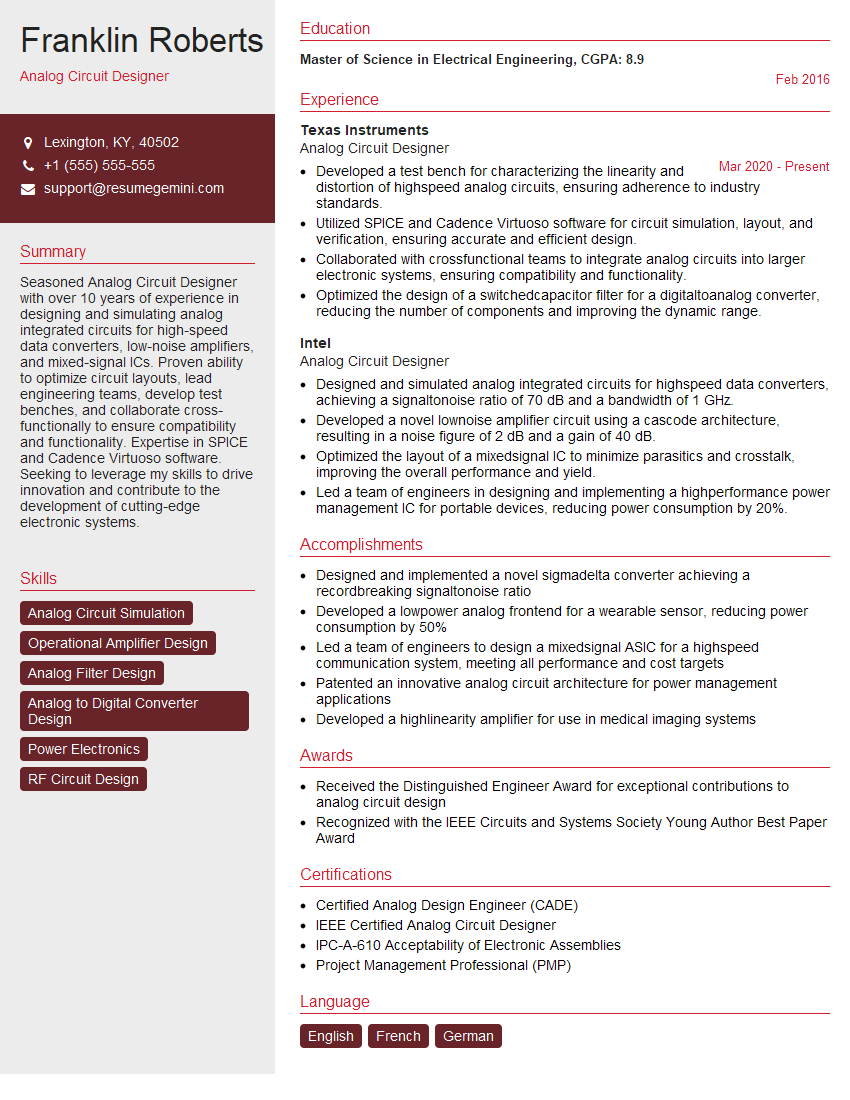

Mastering Custom IC Design opens doors to exciting and high-impact roles within the semiconductor industry, offering significant career growth potential and opportunities for innovation. To maximize your job prospects, it’s essential to present your skills effectively. Creating an ATS-friendly resume is crucial for getting your application noticed by recruiters and hiring managers. We strongly encourage you to leverage ResumeGemini, a trusted resource for crafting compelling and professional resumes. ResumeGemini provides examples of resumes tailored to Custom IC Design to help you create a document that highlights your expertise and secures you interviews.

Explore more articles

Users Rating of Our Blogs

Share Your Experience

We value your feedback! Please rate our content and share your thoughts (optional).

What Readers Say About Our Blog

Hello,

we currently offer a complimentary backlink and URL indexing test for search engine optimization professionals.

You can get complimentary indexing credits to test how link discovery works in practice.

No credit card is required and there is no recurring fee.

You can find details here:

https://wikipedia-backlinks.com/indexing/

Regards

NICE RESPONSE TO Q & A

hi

The aim of this message is regarding an unclaimed deposit of a deceased nationale that bears the same name as you. You are not relate to him as there are millions of people answering the names across around the world. But i will use my position to influence the release of the deposit to you for our mutual benefit.

Respond for full details and how to claim the deposit. This is 100% risk free. Send hello to my email id: [email protected]

Luka Chachibaialuka

Hey interviewgemini.com, just wanted to follow up on my last email.

We just launched Call the Monster, an parenting app that lets you summon friendly ‘monsters’ kids actually listen to.

We’re also running a giveaway for everyone who downloads the app. Since it’s brand new, there aren’t many users yet, which means you’ve got a much better chance of winning some great prizes.

You can check it out here: https://bit.ly/callamonsterapp

Or follow us on Instagram: https://www.instagram.com/callamonsterapp

Thanks,

Ryan

CEO – Call the Monster App

Hey interviewgemini.com, I saw your website and love your approach.

I just want this to look like spam email, but want to share something important to you. We just launched Call the Monster, a parenting app that lets you summon friendly ‘monsters’ kids actually listen to.

Parents are loving it for calming chaos before bedtime. Thought you might want to try it: https://bit.ly/callamonsterapp or just follow our fun monster lore on Instagram: https://www.instagram.com/callamonsterapp

Thanks,

Ryan

CEO – Call A Monster APP

To the interviewgemini.com Owner.

Dear interviewgemini.com Webmaster!

Hi interviewgemini.com Webmaster!

Dear interviewgemini.com Webmaster!

excellent

Hello,

We found issues with your domain’s email setup that may be sending your messages to spam or blocking them completely. InboxShield Mini shows you how to fix it in minutes — no tech skills required.

Scan your domain now for details: https://inboxshield-mini.com/

— Adam @ InboxShield Mini

Reply STOP to unsubscribe

Hi, are you owner of interviewgemini.com? What if I told you I could help you find extra time in your schedule, reconnect with leads you didn’t even realize you missed, and bring in more “I want to work with you” conversations, without increasing your ad spend or hiring a full-time employee?

All with a flexible, budget-friendly service that could easily pay for itself. Sounds good?

Would it be nice to jump on a quick 10-minute call so I can show you exactly how we make this work?

Best,

Hapei

Marketing Director

Hey, I know you’re the owner of interviewgemini.com. I’ll be quick.

Fundraising for your business is tough and time-consuming. We make it easier by guaranteeing two private investor meetings each month, for six months. No demos, no pitch events – just direct introductions to active investors matched to your startup.

If youR17;re raising, this could help you build real momentum. Want me to send more info?

Hi, I represent an SEO company that specialises in getting you AI citations and higher rankings on Google. I’d like to offer you a 100% free SEO audit for your website. Would you be interested?

Hi, I represent an SEO company that specialises in getting you AI citations and higher rankings on Google. I’d like to offer you a 100% free SEO audit for your website. Would you be interested?

good