Every successful interview starts with knowing what to expect. In this blog, we’ll take you through the top Faulty Die Analysis interview questions, breaking them down with expert tips to help you deliver impactful answers. Step into your next interview fully prepared and ready to succeed.

Questions Asked in Faulty Die Analysis Interview

Q 1. Explain the different techniques used in identifying faulty dies.

Identifying faulty dies involves a multi-faceted approach combining visual inspection, electrical testing, and advanced microscopy techniques. The goal is to pinpoint the root cause of failure, whether it’s a manufacturing defect or a design flaw.

- Visual Inspection: This initial step involves carefully examining the die under a microscope for obvious physical defects like cracks, open circuits, shorts, or contamination. Think of it like a doctor’s initial examination – looking for any immediately apparent problems.

- Electrical Testing: This crucial step involves applying various electrical stimuli and measuring the die’s response. We use specialized equipment to test parameters like voltage, current, and capacitance, looking for deviations from expected behavior. For example, a faulty transistor might show abnormally high leakage current.

- Advanced Microscopy: When visual inspection and basic electrical tests aren’t enough, we turn to advanced techniques like optical microscopy, scanning electron microscopy (SEM), and focused ion beam (FIB) for detailed analysis. These techniques allow us to visualize the die’s internal structure and pinpoint the exact location of the failure.

The choice of technique depends on the suspected failure mechanism and the level of detail required. Often, a combination of these methods is employed to build a comprehensive understanding of the failure.

Q 2. Describe your experience with optical microscopy in failure analysis.

Optical microscopy is a cornerstone of my failure analysis workflow. It’s the first line of defense after initial visual inspection, allowing for higher magnification and more detailed examination. I’ve used it extensively to identify defects like scratches, cracks, delamination, and foreign material on the die surface. For instance, in one case, optical microscopy revealed a tiny metal particle bridging two conductive lines, causing a short circuit. The high-resolution images allowed us to precisely locate and document the defect, which was instrumental in determining the root cause and preventing similar failures in future production runs. The technique’s simplicity and speed make it invaluable for quickly assessing a large number of dies.

Q 3. How do you differentiate between process-induced and design-related failures?

Differentiating between process-induced and design-related failures requires a systematic approach. Process-induced failures stem from imperfections during the manufacturing process, while design-related failures are due to flaws in the chip’s design itself. We often use a combination of techniques to reach a conclusion.

- Statistical Analysis: A high failure rate concentrated in a specific area of the die or across multiple dies strongly suggests a process problem. For example, consistent failures in the same bonding pad might indicate a problem with the bonding process.

- Microscopic Examination: Microscopic analysis can reveal physical defects like voids, contamination, or dislocations, indicating a process issue. Conversely, a design flaw might manifest as a layout issue—perhaps a critical connection being too close to the edge of the die—visible under a microscope.

- Electrical Characterization: Unusual electrical parameters might point towards a design flaw. For example, consistent failures under specific operating conditions might hint at an inadequate design margin.

Careful analysis of the failure data, coupled with strong process and design understanding, allows us to confidently attribute failures to their root causes.

Q 4. What are the key metrics used to evaluate the success of faulty die analysis?

The success of faulty die analysis is evaluated using several key metrics. The primary goal is to accurately identify the root cause of failure and provide actionable recommendations for preventing future occurrences.

- Root Cause Identification Accuracy: The most important metric is the accuracy of the root cause determination. Was the identified problem truly the underlying cause of the failure? This often requires verification through experiments or simulations.

- Time to Resolution: Rapid identification of the root cause minimizes downtime and reduces costs. A faster analysis process directly impacts production efficiency.

- Effectiveness of Corrective Actions: The ultimate measure of success is the effectiveness of corrective actions implemented based on the analysis findings. Did those actions reduce or eliminate the failure rate?

- Cost Savings: A successful analysis leads to cost savings by preventing future failures, reducing scrap, and improving overall yield.

These metrics are often tracked and analyzed to continually improve the failure analysis process.

Q 5. Explain your experience with Scanning Electron Microscopy (SEM) and its applications in failure analysis.

Scanning Electron Microscopy (SEM) is a powerful technique I use regularly for high-resolution imaging of the die’s surface and cross-sections. It offers significantly higher magnification than optical microscopy, allowing for the visualization of extremely small features. SEM’s ability to generate high-resolution images is particularly useful in identifying subtle defects, such as minute cracks, voids, or contamination particles invisible under optical microscopes. For example, I once used SEM to detect a tiny void within a metallization layer that was causing intermittent electrical failures. The SEM images provided crucial evidence for understanding the mechanism of failure and guiding corrective actions.

Furthermore, SEM can be used in conjunction with energy-dispersive X-ray spectroscopy (EDS) to determine the elemental composition of materials on the die surface, assisting in identifying contaminants or material anomalies. This capability is essential for diagnosing issues caused by material defects or processing errors.

Q 6. Describe your experience using Focused Ion Beam (FIB) for cross-sectioning and analysis.

Focused Ion Beam (FIB) is an invaluable technique for creating precise cross-sections of the die, allowing for detailed three-dimensional analysis of internal structures. I’ve used FIB extensively to investigate failures occurring within the layers of the die, inaccessible using other methods. FIB’s ability to mill extremely precise cuts allows us to image specific structures and layers with high precision. For instance, in analyzing a failure within a multi-layered capacitor, FIB allowed me to create cross-sections at the point of failure, revealing a delamination between two layers that was causing an open circuit. The resulting images helped identify the underlying root cause—a process parameter deviation during the capacitor’s fabrication.

Beyond cross-sectioning, FIB can also be used for sample preparation for other analytical techniques, such as Transmission Electron Microscopy (TEM), providing even greater resolution and insights into the failure mechanism.

Q 7. How do you interpret data obtained from electrical testing of faulty dies?

Interpreting data from electrical testing of faulty dies requires a deep understanding of both the die’s design and its expected electrical behavior. We typically compare the measured parameters with the expected values based on the die’s specifications. Deviations from expected values can indicate various problems.

- Increased Leakage Current: Higher than expected leakage current in transistors or diodes can suggest damage to the insulating layers or defects in the semiconductor material.

- Reduced Breakdown Voltage: Lower than expected breakdown voltage indicates weakening of the junctions within the die.

- Abnormal Capacitance: Unexpected changes in capacitance can point to physical defects, such as shorts or opens.

- Parametric Shifts: Changes in device parameters (e.g., gain, threshold voltage) beyond acceptable limits might reveal underlying design or process flaws.

A systematic approach, combining electrical measurements with physical analysis techniques, is essential for accurate interpretation. We often rely on statistical analysis of data from multiple samples to distinguish between random variations and systematic problems.

Q 8. What are the common causes of die failures in semiconductor manufacturing?

Die failures in semiconductor manufacturing stem from a variety of sources, broadly categorized as process-related, design-related, and material-related issues.

- Process-related failures: These are often caused by imperfections during the manufacturing process itself. Examples include contamination (particles, chemicals), etching defects (under-etching, over-etching), lithography issues (misalignment, insufficient resolution), and problems during deposition (voids, thin spots). Imagine baking a cake – if the oven temperature is inconsistent, you get a poorly baked cake, similarly, variations in the manufacturing process can create defects.

- Design-related failures: These failures arise from flaws in the chip’s design. These could be layout issues, such as short circuits or open circuits due to design errors, incorrect transistor sizing leading to instability, or poor power distribution resulting in overheating. A poorly designed blueprint for a house will lead to structural problems; similarly, a bad chip design leads to faulty functionality.

- Material-related failures: These are linked to the quality of the materials used in the manufacturing process. This can include defects in the silicon wafer itself (e.g., dislocations, impurities), problems with the interconnects (e.g., electromigration, stress voiding), or issues with the packaging materials (e.g., cracks, delamination). Think of building a house with weak bricks; it won’t be stable. Similarly, flawed base materials will create weaknesses in the chip.

Understanding the root cause allows for targeted corrective actions, from tweaking process parameters to revising the chip design or sourcing higher-quality materials.

Q 9. How do you determine the root cause of a failure based on failure analysis results?

Determining the root cause of a die failure involves a systematic approach, combining visual inspection, electrical testing, and advanced analytical techniques. The process typically starts with non-destructive tests, such as electrical characterization (to identify the faulty circuit section) and optical microscopy (to find visible defects). If these initial tests don’t yield a clear answer, more sophisticated techniques are employed.

- Cross-sectioning and Scanning Electron Microscopy (SEM): Allows for detailed visualization of internal structures and defects. This is crucial for identifying physical flaws like voids, cracks, or metal migration.

- Energy Dispersive X-ray Spectroscopy (EDS): Coupled with SEM, EDS identifies the elemental composition at specific points, helping determine contamination or material degradation.

- Focused Ion Beam (FIB): Used for site-specific preparation of samples for SEM and Transmission Electron Microscopy (TEM) analysis providing high-resolution images and compositional data.

- Failure Mode and Effects Analysis (FMEA): A systematic approach to identify potential failure modes and their impact, aiding in root cause identification and prevention.

By carefully interpreting the data from these various methods, we can create a ‘failure story,’ step by step tracing the events that led to the failure. For instance, finding a void in the interconnect metallization via SEM, coupled with EDS indicating contamination at that point, might lead to the conclusion that the void was caused by particle contamination during the metal deposition step.

Q 10. Describe your experience with statistical analysis techniques in failure analysis.

Statistical analysis plays a crucial role in interpreting failure analysis results, allowing us to move beyond individual case studies and draw more general conclusions about the failure mechanism. My experience involves the application of several techniques:

- Control Charts: Monitoring process parameters over time to identify trends and deviations from acceptable limits. This is crucial for identifying potential failures before they manifest as a full-blown die failure.

- Statistical Process Control (SPC): Used to monitor and control the manufacturing process, reducing variability and improving product yield. Identifying out-of-control points in a process control chart helps pinpoint stages prone to defect generation.

- Design of Experiments (DOE): Used to systematically investigate the influence of process parameters on failure rates. This enables the identification of critical parameters and the optimization of the manufacturing process to reduce failures.

- Regression Analysis: Used to analyze the relationship between different factors (process parameters, material properties, etc.) and the failure rate. This can help identify critical factors contributing to the failure mechanism.

For example, by applying regression analysis to a dataset linking failure rates to various process parameters, we might find a strong correlation between substrate temperature and the occurrence of voids in a specific metal layer, directly guiding process optimization.

Q 11. Explain the importance of documentation in the failure analysis process.

Meticulous documentation is paramount in failure analysis. It ensures reproducibility, facilitates collaboration, and protects intellectual property. A comprehensive record preserves the integrity and traceability of the analysis process.

- Detailed Lab Notebook: Recording all experimental procedures, observations, and results in a detailed manner. This should include dates, times, equipment used, and any deviations from standard procedures.

- Digital Images and Data: Storing all images (optical microscopy, SEM, TEM) and analytical data (EDS, etc.) securely with appropriate metadata. This allows for review and re-analysis later, perhaps even by other engineers.

- Formal Reports: Summarizing the findings of the failure analysis in a clear, concise report that includes the methodology, results, conclusions, and recommendations. This serves as a formal record of the investigation.

- Version Control: Using a version control system (like Git) for all analysis reports and data, allowing for tracking changes and collaborative editing.

A well-documented failure analysis not only helps in resolving the immediate problem but also serves as a valuable source of knowledge for future investigations and process improvements. Imagine a detective’s case file – a detailed record allows for thorough understanding and effective conclusions, Similarly, this is critical in our failure analysis.

Q 12. How do you prioritize multiple faulty die analysis requests?

Prioritizing faulty die analysis requests requires a strategic approach that considers several factors:

- Severity of the Failure: Failures affecting critical functionalities or high-volume products are given higher priority.

- Urgency of the Situation: Requests related to immediate production issues or customer escalations demand immediate attention.

- Potential Impact: Analysis of failures that could have widespread implications are given priority over isolated issues.

- Resource Availability: The available time and resources (equipment, personnel) also need to be considered.

A common approach is a weighted scoring system that assigns scores to each factor, generating a total score used for prioritization. Think of a hospital triage system where the most critical cases receive priority treatment; similarly, this system helps efficiently allocate resources.

Q 13. Describe a situation where you had to troubleshoot a complex failure mechanism.

In one instance, we encountered a high failure rate in a new generation of power amplifiers. Initial electrical tests pointed to a failure in the output stage but revealed no obvious physical defects under optical microscopy. We then employed cross-sectioning and SEM, eventually uncovering microscopic cracks at the interface between the silicon substrate and the metallization layer. Further EDS analysis revealed an unexpected high concentration of oxygen at the interface.

The root cause was traced to a process modification introduced during the manufacturing of the substrates. A slight change in the oxidation process had created these weak interfaces, leading to cracks under the stress of high power operation. This finding not only solved the immediate problem but allowed us to implement process improvements to prevent the issue from recurring. This highlighted the importance of a thorough investigative process beyond basic fault localization and the necessity of high-resolution imaging and compositional analysis.

Q 14. How do you handle disagreements with other engineers regarding failure analysis conclusions?

Disagreements are inevitable in a technical field like failure analysis. I believe in a collaborative approach that prioritizes data and evidence. When disagreements arise, I advocate for:

- Open Communication: Clearly expressing our perspectives and supporting them with data and evidence.

- Data Review: Jointly reviewing all data and analyses, ensuring that everyone has access to the same information.

- Additional Testing: If needed, conducting further tests to resolve the points of contention. This might involve repeating experiments, running statistical tests on a larger dataset, or trying different analysis techniques.

- Expert Consultation: Seeking expert advice from senior engineers or external specialists if the disagreement cannot be resolved internally.

- Documentation: Carefully documenting the points of disagreement and how they were resolved, with an emphasis on mutual agreement on the final conclusion.

Ultimately, the goal is to arrive at the most accurate and robust conclusion based on the available evidence, even if it means modifying initial hypotheses. The focus is always on objective evidence, and using a respectful and collaborative approach fosters a healthy engineering environment where solutions, not egos, are prioritized.

Q 15. Explain your understanding of Design of Experiments (DOE) and its role in failure analysis.

Design of Experiments (DOE) is a powerful statistical methodology used to plan experiments efficiently and analyze the results to understand the relationship between different factors and a response variable. In failure analysis, we use DOE to systematically investigate the root causes of die failures. Imagine you’re trying to bake a cake – DOE helps you figure out which ingredient (factor) affects the cake’s texture (response) the most. We might change the baking temperature, mixing time, or amount of flour (factors) in a controlled manner and observe how these changes affect the failure rate (response).

For example, if we suspect that a specific process parameter, such as the temperature of a particular diffusion step, impacts the yield of integrated circuits, a DOE would allow us to systematically vary this temperature while holding other parameters constant. By analyzing the results, we can determine the optimal temperature setting that minimizes failures and maximizes yield. Common DOE techniques include factorial designs and Taguchi methods, which help to efficiently explore the design space and identify significant factors.

Career Expert Tips:

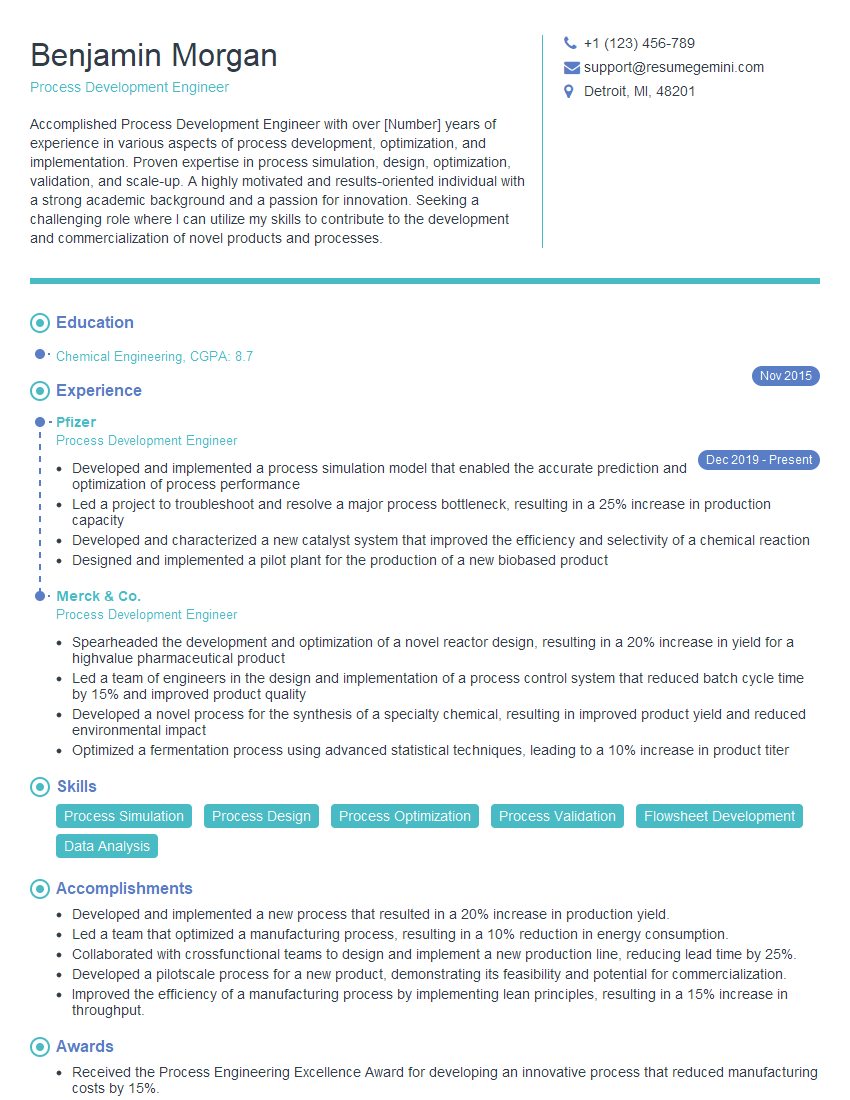

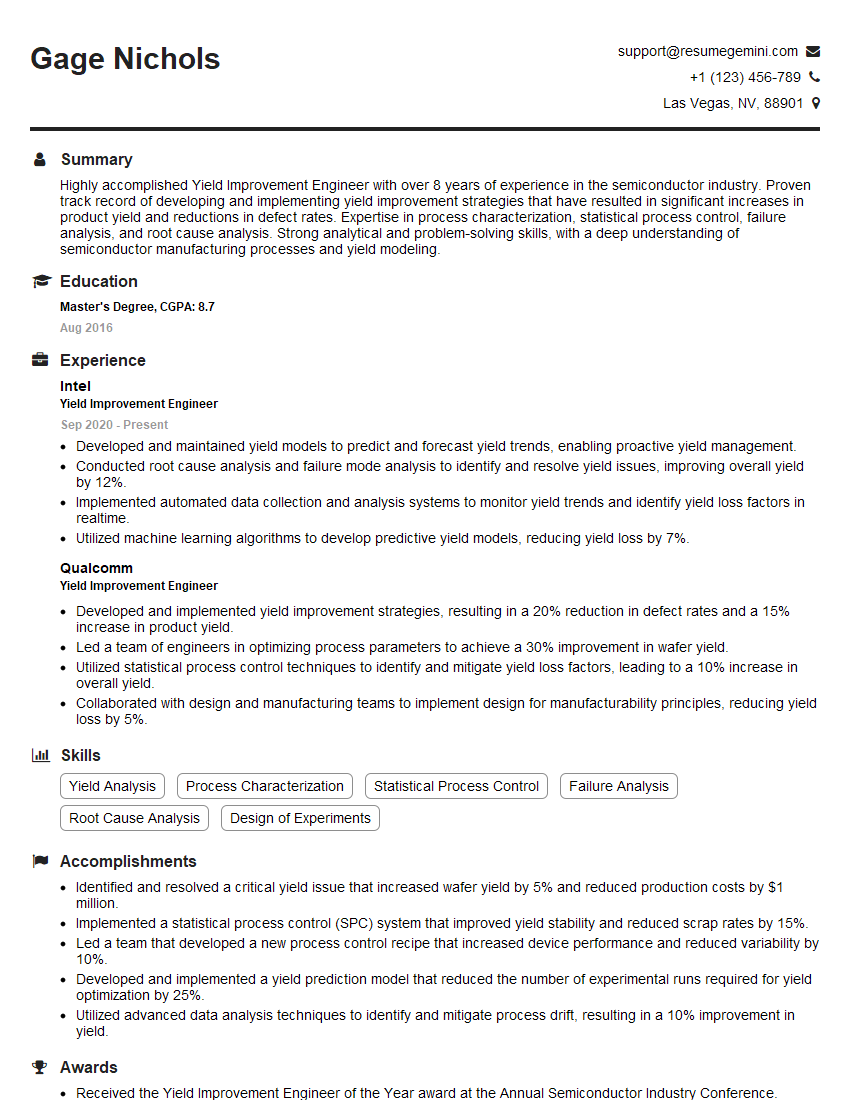

- Ace those interviews! Prepare effectively by reviewing the Top 50 Most Common Interview Questions on ResumeGemini.

- Navigate your job search with confidence! Explore a wide range of Career Tips on ResumeGemini. Learn about common challenges and recommendations to overcome them.

- Craft the perfect resume! Master the Art of Resume Writing with ResumeGemini’s guide. Showcase your unique qualifications and achievements effectively.

- Don’t miss out on holiday savings! Build your dream resume with ResumeGemini’s ATS optimized templates.

Q 16. What software tools are you proficient in for failure analysis and data interpretation?

My proficiency encompasses a range of software tools vital for failure analysis and data interpretation. I’m highly skilled in using specialized software packages such as:

- Scanning Electron Microscopy (SEM) software: For analyzing images and data obtained from SEM analysis, such as identifying physical defects and measuring dimensions.

- Focused Ion Beam (FIB) software: For controlling the FIB system during cross-sectioning and sample preparation. This includes software that allows for 3D reconstruction from FIB-SEM data.

- Data analysis software: Packages like JMP, Minitab, and R are extensively used for statistical analysis of failure data, DOE analysis, and creating visualizations to interpret trends and identify root causes. I use these tools to conduct statistical process control (SPC) analysis and regression analysis.

- Circuit simulation tools: Software like SPICE is used for electrical simulation to model circuit behavior and identify potential failure modes before physical testing.

Furthermore, my expertise extends to image processing software for enhancing micrographs and other visual data acquired during the failure analysis process.

Q 17. Describe your experience with different types of semiconductor packaging and their impact on failure analysis.

My experience spans a wide variety of semiconductor packaging technologies, each presenting unique challenges and considerations during failure analysis. Different packaging types can significantly influence failure mechanisms and the difficulty of identifying the root cause.

- Wire-bonded packages: These are susceptible to wire breakage, bond pad failures, and delamination issues. Failure analysis requires careful decapsulation and microscopic inspection of the bond wires and connections.

- Flip-chip packages: These present challenges with underfill inspection and solder ball analysis. Voiding in the underfill or solder joints is a major concern that requires sophisticated imaging and analysis techniques.

- Ball Grid Array (BGA) packages: These packages require specialized equipment and techniques for decapsulation and inspection of the numerous solder balls. X-ray inspection is often crucial to detect hidden defects.

- System-in-Package (SiP): These highly integrated packages present the most complex challenges, requiring a combination of imaging, electrical probing and sometimes even deprocessing to isolate failures.

Understanding the construction and potential failure points of each packaging type is critical to developing an effective analysis strategy.

Q 18. How do you ensure the accuracy and reliability of your failure analysis results?

Ensuring the accuracy and reliability of failure analysis results is paramount. We employ a multi-pronged approach:

- Multiple Analysis Techniques: We utilize a combination of techniques, such as optical microscopy, SEM, FIB, X-ray inspection, and electrical testing to verify findings from different perspectives. This cross-validation minimizes errors and biases.

- Controlled Environment: All analysis is conducted in a controlled environment to minimize contamination and ensure accurate measurements. ESD precautions are always strictly followed.

- Calibration and Verification: Our equipment is regularly calibrated and verified against standards to maintain accuracy and precision. Control samples are frequently analyzed to monitor instrument performance.

- Documented Procedures: We meticulously document each step of the analysis process, including sample handling, test parameters, and results. This ensures traceability and reproducibility.

- Cross-Checking and Peer Review: Results are cross-checked by multiple engineers, and a peer review process is often employed to ensure the integrity and validity of conclusions.

This rigorous approach minimizes errors and enhances the reliability of our findings.

Q 19. How familiar are you with various failure mechanisms such as electromigration, voiding, and hot carrier effects?

I am very familiar with various failure mechanisms that can impact semiconductor devices. These include:

- Electromigration: The gradual movement of metal ions in conductors due to high current densities. This can lead to open circuits or shorts.

- Voiding: The formation of voids or empty spaces in metal interconnects or solder joints. These voids can weaken the connection and lead to failures.

- Hot Carrier Effects: The degradation of transistors due to high-energy carriers impacting the gate oxide. This can result in performance degradation or device failure.

- Time-Dependent Dielectric Breakdown (TDDB): Degradation of the gate oxide over time under stress, leading to leakage current increase and potential failure.

- Stress migration: The movement of dislocations in the material, resulting in plastic deformation and potential cracking.

Understanding these mechanisms is vital in diagnosing the root cause of a failure and implementing corrective actions.

Q 20. Explain your understanding of the relationship between process parameters and die yield.

Process parameters significantly influence die yield. A die’s yield refers to the percentage of successfully functioning dies produced from a wafer. Variations in process parameters directly affect the defect density on the wafer. Imagine a manufacturing line producing cars—variations in the assembly process, like incorrect tightening of bolts, increase the rate of faulty cars (low yield).

Examples of process parameters that affect die yield include:

- Temperature variations: Inconsistent temperatures during deposition or etching steps can lead to variations in layer thicknesses or etching profiles, increasing defect rates.

- Photolithographic alignment: Imperfect alignment of photomasks during lithographic processes can result in misalignment of transistors and interconnects, causing failures.

- Etch depths and selectivities: Inaccurate etch depths or poor selectivities lead to under- or over-etching, impacting device performance and yield.

- Implantation dose and energy: Incorrect implantation parameters can cause doping irregularities, affecting transistor behavior and leading to failures.

By carefully monitoring and controlling process parameters, we can minimize defects and increase the yield of good dies. Statistical process control (SPC) charts help to monitor and manage these parameters effectively.

Q 21. How do you use failure analysis data to drive process improvements?

Failure analysis data is crucial for driving process improvements. Analyzing the root causes of failures allows us to identify weaknesses in the manufacturing process and implement targeted improvements. For instance, if a high number of failures are linked to a specific process step, such as a particular photolithography stage, we might optimize parameters, such as exposure time or mask alignment, to reduce defect density.

The data informs several key areas:

- Process Parameter Optimization: Identifying the impact of each parameter on yield and guiding adjustments for optimal performance. This often uses statistical methods like DOE to find optimal settings.

- Equipment Maintenance: If failures correlate with specific equipment, the data helps prioritize maintenance and calibration, ensuring equipment is functioning optimally.

- Material Selection: Failure analysis might reveal material weaknesses, prompting the selection of alternative materials better suited for the manufacturing process.

- Design Improvements: The identification of failures due to design flaws leads to design changes for improved reliability.

A continuous feedback loop, using failure analysis data to improve the process, is fundamental to achieving high yields and reliable products.

Q 22. Describe your experience with creating reports and presentations summarizing failure analysis findings.

Creating comprehensive reports and presentations summarizing failure analysis findings is crucial for effective communication and problem-solving within a semiconductor manufacturing environment. My process begins with meticulously documenting all findings from each analysis technique employed, including detailed images (optical microscopy, SEM, etc.), measurements, and observations. I then organize this data into a logical narrative that progresses from initial observations to the final root cause conclusion.

For instance, in analyzing a batch of faulty memory chips exhibiting data retention issues, my report would start with a description of the failure symptoms and the number of affected units. It would then detail the steps taken during physical failure analysis, like cross-sectioning and defect localization, followed by electrical testing data showing the malfunctioning components. Finally, a conclusive section summarizes the root cause (e.g., a specific manufacturing process defect) and provides recommendations for corrective actions. This is often presented visually with clear diagrams, charts, and high-quality micrographs to ensure quick comprehension. I tailor the report’s complexity and depth depending on the audience; a technical team requires detailed data, while management requires a concise executive summary focusing on impact and solutions.

Presentations are crafted similarly, emphasizing visual aids and concise summaries for impactful communication. I frequently utilize interactive elements such as 3D models or animations when presenting to larger audiences to improve engagement and understanding of complex 3D structures.

Q 23. How do you collaborate with cross-functional teams to resolve faulty die issues?

Collaborating effectively with cross-functional teams is paramount in resolving faulty die issues. It requires clear communication, active listening, and a willingness to leverage the diverse expertise within the organization. My approach centers around establishing a well-defined communication strategy early on. This involves regular meetings with representatives from different departments, including process engineering, design engineering, and manufacturing, to ensure a shared understanding of the problem.

For example, if we encounter yield issues in a specific production line, I’ll work with the process engineers to review their process parameters and identify potential deviations. Simultaneously, I’ll collaborate with the design engineers to understand the chip architecture and identify critical areas sensitive to manufacturing variations. This synergistic approach ensures that no stone is left unturned, and we can efficiently pinpoint the root cause of the failure. To facilitate information sharing, I utilize collaborative tools like shared online workspaces and databases to ensure everyone has access to updated findings and analysis. This fosters transparency and accelerates the troubleshooting process.

Q 24. What are some common challenges encountered in performing faulty die analysis?

Faulty die analysis presents several challenges, some of which are inherent to the complexity of modern integrated circuits. One significant hurdle is the minute size of defects; locating and characterizing them requires advanced microscopic techniques and highly skilled analysts. Another challenge involves interpreting the data obtained from various analysis methods. The root cause is not always directly apparent, requiring careful correlation of results from different techniques (optical microscopy, scanning electron microscopy (SEM), focused ion beam (FIB), energy-dispersive X-ray spectroscopy (EDS), etc.).

Additionally, the analysis can be time-consuming and resource-intensive, particularly when dealing with complex failures. There’s also the challenge of dealing with rare or unique failure mechanisms that require extensive research and potentially the development of novel analysis techniques. The possibility of destructive analysis also adds a layer of complexity, as it often necessitates carefully planning to minimize sample damage and maximize information gained. Finally, maintaining the integrity of the sample throughout the analysis process is crucial to prevent further damage or contamination that could lead to misinterpretations.

Q 25. Describe your experience with different types of failure analysis techniques (e.g., physical, electrical, chemical).

My experience encompasses a wide range of failure analysis techniques, both physical and electrical. I am proficient in using optical microscopy for initial defect localization and visual inspection. Scanning electron microscopy (SEM) provides higher resolution imaging for detailed defect characterization. I routinely employ focused ion beam (FIB) milling for cross-sectioning and sample preparation for more in-depth analysis, including Transmission Electron Microscopy (TEM) sample preparation. Chemical analysis techniques such as energy-dispersive X-ray spectroscopy (EDS) and Auger electron spectroscopy (AES) allow me to identify the elemental composition of defects and materials.

Electrical testing is crucial for characterizing the electrical behavior of the faulty die. I have extensive experience using techniques like curve tracing, electromigration testing, and in-situ electrical measurements during FIB cross-sectioning to pin down failing circuit elements. The choice of technique depends heavily on the nature of the failure and the information needed; sometimes a combination of physical and electrical methods is necessary to obtain a complete understanding.

For example, a memory cell failure might involve initial optical inspection to identify physical damage, followed by SEM to examine the damage detail, and finally FIB cross-sectioning and EDS to reveal the underlying material changes that caused the malfunction.

Q 26. How do you stay current with the latest advancements in failure analysis technology?

Keeping abreast of the latest advancements in failure analysis technology is essential for maintaining a high level of expertise. I achieve this through several avenues. Regular attendance at conferences and workshops like the International Symposium for Testing and Failure Analysis (ISTFA) allows for direct interaction with leading experts and exposure to cutting-edge techniques.

I actively subscribe to and read relevant scientific journals and publications, including those focusing on materials science, semiconductor physics, and microelectronics. Online resources like IEEE Xplore and professional society websites provide access to the latest research papers and technical articles. I also actively engage with online communities and professional networks dedicated to failure analysis, exchanging information and insights with peers and industry specialists. Finally, I participate in internal training programs and workshops focused on new equipment and analytical methodologies within my company to stay current with our in-house capabilities.

Q 27. Explain your understanding of root cause analysis techniques and their application in failure analysis.

Root cause analysis (RCA) is the cornerstone of effective failure analysis. It’s a systematic approach used to identify the underlying causes of failures, going beyond the immediate symptoms to pinpoint the fundamental issue. Several RCA techniques exist, and the choice depends on the complexity of the failure and available data.

One common method is the ‘5 Whys’ technique, where you repeatedly ask ‘Why?’ to drill down to the root cause. For example, if a circuit fails due to overheating, the 5 Whys might lead to identifying inadequate heat sinking as the root cause. However, this method is best suited for simple failures. More structured approaches include Fault Tree Analysis (FTA), where possible failure modes are mapped out to identify the most likely root cause combinations. Fishbone diagrams (Ishikawa diagrams) help visualize potential causes categorized by different factors (materials, processes, equipment, etc.).

In my work, I often use a combination of techniques, starting with a visual inspection and initial observations to formulate hypotheses. I then utilize the appropriate analytical techniques, both electrical and physical, to test and validate these hypotheses. Once sufficient data is collected, I use structured RCA approaches to consolidate the information, pinpoint the root cause, and propose effective corrective actions. This ensures not only that the immediate problem is resolved but also that similar failures are prevented in the future.

Key Topics to Learn for Faulty Die Analysis Interview

- Statistical Process Control (SPC) in Semiconductor Manufacturing: Understanding control charts, process capability analysis, and their application in identifying faulty dies.

- Failure Analysis Techniques: Familiarize yourself with various methods like optical microscopy, scanning electron microscopy (SEM), and energy-dispersive X-ray spectroscopy (EDX) for root cause identification.

- Defect Classification and Root Cause Identification: Learn to categorize defects (e.g., open circuits, shorts, contamination) and systematically determine their origins.

- Data Analysis and Interpretation: Develop proficiency in analyzing large datasets related to yield, defect rates, and failure modes to pinpoint trends and patterns.

- Electrical Testing and Measurement Techniques: Understand the principles behind various electrical tests used to characterize faulty dies and their implications.

- Yield Improvement Strategies: Explore methods for enhancing manufacturing processes and reducing the incidence of faulty dies, such as process optimization and defect prevention.

- Documentation and Reporting: Practice clearly communicating your findings through detailed reports and presentations, effectively conveying technical information to diverse audiences.

- Problem-Solving Methodologies: Master structured problem-solving approaches (e.g., 8D, DMAIC) to effectively tackle complex failure analysis challenges.

Next Steps

Mastering Faulty Die Analysis opens doors to exciting career opportunities in the semiconductor industry, offering high demand and excellent growth potential. A strong resume is crucial for showcasing your skills and experience to potential employers. To significantly increase your chances of landing your dream job, create an ATS-friendly resume that highlights your technical abilities and relevant experience. ResumeGemini is a trusted resource that can help you build a professional and impactful resume tailored to the semiconductor industry. Examples of resumes specifically tailored for Faulty Die Analysis roles are available within ResumeGemini to guide you. Invest in your future—invest in a strong resume.

Explore more articles

Users Rating of Our Blogs

Share Your Experience

We value your feedback! Please rate our content and share your thoughts (optional).

What Readers Say About Our Blog

good