Every successful interview starts with knowing what to expect. In this blog, we’ll take you through the top Semiconductor Packaging interview questions, breaking them down with expert tips to help you deliver impactful answers. Step into your next interview fully prepared and ready to succeed.

Questions Asked in Semiconductor Packaging Interview

Q 1. Explain the different types of semiconductor packaging.

Semiconductor packaging encompasses a wide variety of techniques aimed at protecting and connecting integrated circuits (ICs) to the outside world. The choice of package depends heavily on the application, performance requirements, and cost constraints. Here are some key types:

- Through-Hole Packaging: These older packages, like DIP (Dual In-line Package) and SIP (Single In-line Package), have pins that pass through holes in a printed circuit board (PCB). They’re relatively simple and inexpensive, but less suitable for high-density applications.

- Surface Mount Packages (SMPs): Far more prevalent today, these packages feature leads (or pads) that are soldered directly onto the surface of the PCB. Examples include QFP (Quad Flat Package), SOIC (Small Outline Integrated Circuit), and BGA (Ball Grid Array). SMPs allow for higher density and automation-friendly assembly.

- Leadless Packages: Designed for extremely high density, these packages eliminate leads entirely, often using solder bumps for connection. Examples include chip-scale packages (CSPs) and flip-chip packages. They excel in miniaturization.

- Advanced Packaging: This category encompasses more complex techniques like system-in-package (SiP), where multiple chips are integrated into a single package, and 3D packaging, where chips are stacked vertically to increase density and performance.

Choosing the right package type is a critical design decision, influenced by factors such as I/O count, power dissipation, cost, and board space limitations.

Q 2. Describe the advantages and disadvantages of various packaging materials (e.g., plastic, ceramic).

Packaging material selection involves a trade-off between cost, performance, and reliability.

- Plastic Packaging (e.g., Epoxy molding compounds): These are cost-effective, offer good moisture resistance, and are widely used for many applications. However, they may offer less thermal conductivity than ceramic, leading to potential overheating issues in high-power devices. They also may have slightly lower mechanical strength.

- Ceramic Packaging: Ceramic packages offer superior thermal conductivity, enabling better heat dissipation for high-power devices. They exhibit higher mechanical strength and better hermeticity (ability to prevent moisture and other contaminants from entering), making them ideal for harsh environments. However, they are significantly more expensive than plastic packages and more brittle.

- Other Materials: Other materials like metal (e.g., copper, aluminum) are increasingly used for heat sinks or as part of advanced packaging solutions to improve thermal management. They can provide excellent heat dissipation but often require more complex manufacturing processes.

For example, a high-power processor might favor a ceramic package for optimal heat dissipation, while a low-power sensor might use a cost-effective plastic package. The choice is determined by a careful analysis of the device’s thermal requirements, reliability goals, and budget.

Q 3. What are the key challenges in miniaturizing semiconductor packages?

Miniaturizing semiconductor packages presents significant engineering challenges:

- Signal Integrity: As packages shrink, the distance between signal traces decreases, increasing the risk of crosstalk and signal degradation. Advanced design techniques and materials are needed to mitigate these effects.

- Thermal Management: Higher density leads to increased power dissipation in smaller areas, demanding better heat dissipation solutions. This often involves innovative thermal vias, heat spreaders, and advanced packaging materials.

- Manufacturing Challenges: Precisely assembling and testing ever-smaller components requires advanced manufacturing techniques and precision equipment, which can be expensive and complex.

- Reliability: Smaller packages can be more susceptible to mechanical stress and damage during handling and assembly. Robust design and materials are crucial to ensure reliability.

- Cost: Advanced miniaturization techniques often come with increased manufacturing costs.

The trend toward miniaturization is driven by the demand for smaller, more powerful, and energy-efficient electronic devices. Addressing these challenges requires innovative materials, advanced manufacturing processes, and sophisticated design techniques.

Q 4. How does thermal management impact package design and selection?

Thermal management is paramount in semiconductor packaging, as excessive heat can lead to device failure and reduced lifespan. The design and selection of the package must account for efficient heat dissipation. This involves:

- Material Selection: Choosing materials with high thermal conductivity (like ceramic or metal) is vital for heat transfer away from the die.

- Package Design: Features like heat spreaders, thermal vias, and underfill are incorporated to enhance heat dissipation. The package shape and size also play a crucial role in efficient heat transfer.

- Heat Sinks: External heat sinks, often made of aluminum or copper, are frequently attached to packages to further improve heat dissipation, especially for high-power devices.

- Cooling Solutions: Active cooling solutions such as fans or liquid cooling may be necessary for high-power applications to maintain optimal operating temperatures.

For instance, a high-performance graphics card relies heavily on efficient thermal management techniques because of the high power consumption of the GPU. Inadequate thermal management would lead to throttling or even irreversible damage to the device.

Q 5. Explain the role of underfill in semiconductor packaging.

Underfill is a low-viscosity epoxy material applied beneath the surface mount package (typically a BGA) to improve the package’s reliability and performance. Its primary role is to:

- Stress Reduction: Underfill fills the gap between the package and the PCB, reducing the stress exerted on the solder joints during thermal cycling. This is crucial as repeated heating and cooling cause expansion and contraction, which can lead to solder joint failures.

- Improved Thermal Conductivity: Some underfill materials enhance thermal conductivity, allowing for better heat transfer from the die to the PCB and ultimately to a heat sink.

- Moisture Protection: Underfill provides a barrier against moisture ingress, protecting the sensitive components inside the package from corrosion and degradation.

Think of underfill as a shock absorber and sealant for the package, contributing significantly to its long-term reliability. Its application is a critical step in the packaging process, particularly for packages operating in harsh environments or subjected to significant thermal cycling.

Q 6. Describe the process of wire bonding and its limitations.

Wire bonding is a critical process in semiconductor packaging where tiny gold or aluminum wires are used to make electrical connections between the die pads and the package leads. It’s a mature technology but still widely used.

- Thermocompression Bonding: This method uses heat and pressure to create a metallurgical bond between the wire and the die pad.

- Ultrasonic Bonding: This technique uses ultrasonic vibrations to create a bond through plastic deformation of the wire and the pad.

Limitations: Wire bonding has several limitations:

- Parasitic Inductance and Capacitance: The wires introduce parasitic inductance and capacitance that can affect signal integrity at higher frequencies.

- Mechanical Stress: Wire bonds are susceptible to mechanical stress and fatigue, particularly during thermal cycling.

- Limited I/O Density: The relatively large size of wire bonds limits the number of connections that can be made in a given area.

- Manual/Semi-Automated Processes: The process, even in automated settings, often has higher error rates compared to other methods.

As a result of these limitations, wire bonding is being gradually replaced by other interconnect technologies like flip-chip packaging for applications demanding higher I/O count, higher speed, and improved reliability.

Q 7. What are the different types of flip-chip packaging?

Flip-chip packaging is a technique where the chip is mounted upside down, with its contact pads facing the substrate. The connections are made using solder bumps directly between the chip pads and the substrate.

- Controlled Collapse Chip Connection (C4): This is a common flip-chip technology where solder bumps are reflowed to create connections. It’s cost-effective and widely used.

- Anisotropic Conductive Film (ACF): ACF utilizes a polymer film with conductive particles to create the electrical connections. It offers benefits such as lower cost and less thermal stress, especially suited for flexible substrates.

- Copper Pillar Bumping: Using copper pillars instead of solder bumps offers higher reliability and better electrical performance. This technology is preferred for high-performance applications.

- Through-Silicon Vias (TSVs): TSVs allow for connections through the silicon die itself, enabling 3D stacking of chips. This approach is particularly significant for high-density, high-performance applications like high-bandwidth memory.

The choice of flip-chip technology depends on the specific application requirements, trade-offs between cost, performance, and reliability. Flip-chip offers advantages in terms of reduced package size, improved thermal performance, and higher I/O density, making it a preferred choice for many high-end applications.

Q 8. Explain the concept of system-in-package (SiP).

System-in-Package (SiP) is a miniaturized electronic system where multiple components, including integrated circuits (ICs), passive components (resistors, capacitors), and even antennas, are integrated into a single package. Think of it like a tiny, self-contained circuit board. Instead of having separate chips and components soldered onto a larger PCB, everything is assembled and interconnected within one compact unit. This approach significantly reduces the size and weight of the final product, while improving performance and reliability.

For example, a SiP might integrate a microprocessor, memory chips, and radio frequency (RF) components for a smart wearable device. This allows for a smaller, more energy-efficient device compared to a design using a separate PCB.

- Advantages: Smaller size, reduced weight, improved performance, cost-effective for smaller volumes, simplified assembly.

- Disadvantages: Increased design complexity, potentially higher cost for large volumes, limited component choice depending on the package size.

Q 9. What are the key considerations for package reliability testing?

Key considerations for package reliability testing center around ensuring the package can withstand the stresses of manufacturing, transportation, and operation over its projected lifetime. We need to mimic real-world conditions to predict long-term performance and failure rates.

- Environmental Stress: Testing includes temperature cycling (rapid changes in temperature), thermal shock (sudden temperature changes), humidity testing, and mechanical shock/vibration (simulating drops or vibrations during transportation). These tests evaluate the package’s ability to withstand harsh environmental conditions.

- Electrical Stress: This involves testing for electrical overstress (EOS) and electrostatic discharge (ESD) robustness. We also measure parameters such as resistance, capacitance, and signal integrity over time and under stress.

- Life Testing: Accelerated life testing involves subjecting packages to extreme conditions (e.g., high temperature, high humidity) to accelerate aging and predict the long-term reliability. This allows us to assess the failure rate and estimate the product’s Mean Time To Failure (MTTF).

- Statistical Analysis: Data from these tests are statistically analyzed to determine reliability metrics like failure rate, MTTF, and B10 life (the time at which 10% of the population is expected to fail). This helps us establish confidence levels regarding the product’s reliability.

For instance, a mobile phone’s SiP will be rigorously tested to ensure it survives drops, temperature fluctuations, and long-term use without significant performance degradation.

Q 10. Describe common failure mechanisms in semiconductor packages.

Several failure mechanisms can affect semiconductor packages. These mechanisms often interrelate, leading to complex failure scenarios.

- Delamination: Separation of layers within the package (e.g., die from substrate, molding compound from die). This can be caused by thermal stress or moisture ingress.

- Wire Bond Failure: Failure of the tiny wires connecting the die to the package leads, caused by fatigue, corrosion, or mechanical stress.

- Die Cracking: Internal cracks within the die itself, often caused by mechanical stress or thermal cycling.

- Intermetallic Growth: Formation of brittle intermetallic compounds at the interface between different materials in the package, leading to decreased bond strength and eventually failure.

- Corrosion: Chemical degradation of metallic components within the package, often accelerated by moisture or high temperatures. This can impact wire bonds and lead frames.

- Mold Compound Cracking: Cracks in the plastic molding compound, possibly due to thermal stress or moisture absorption, compromising package integrity.

Understanding these failure mechanisms is critical for designing more reliable and robust packages.

Q 11. How do you perform failure analysis on a packaged device?

Failure analysis on a packaged device is a systematic process to identify the root cause of failure. It often involves a combination of techniques:

- Visual Inspection: A careful visual examination under a microscope to identify any external defects, such as cracks, delamination, or corrosion.

- X-ray Inspection: Non-destructive imaging technique to inspect internal structures, revealing delamination, cracks, or voids.

- Scanning Acoustic Microscopy (SAM): Detects internal voids and delaminations by measuring sound wave reflections.

- Cross-Sectioning: Preparing a cross-section of the package to reveal the internal structure and identify failure locations. Followed by microscopic inspection (optical or electron microscopy).

- Electrical Testing: Measuring electrical parameters to identify the failing component or connection.

- Chemical Analysis: Employing techniques like Energy-Dispersive X-ray Spectroscopy (EDX) to determine the chemical composition of materials and identify corrosion products.

The specific techniques used depend on the suspected failure mechanism. A systematic approach, careful documentation, and knowledge of package construction are essential for effective failure analysis.

Q 12. Explain the importance of hermetic sealing in semiconductor packaging.

Hermetic sealing is critical for maintaining the integrity and long-term reliability of semiconductor packages, particularly for high-reliability applications such as aerospace or automotive. It involves creating a completely airtight and moisture-proof seal to protect the internal components from the environment.

Moisture ingress (water entering the package) can cause corrosion, electromigration, and other failure mechanisms. Hermetic sealing prevents this, extending the life and reliability of the device. This is achieved through techniques such as welding, brazing, or glass sealing, depending on the package type.

Think of it like preserving food in a vacuum-sealed bag—the seal prevents oxidation and spoilage. Similarly, hermetic sealing prevents degradation of the sensitive semiconductor components within the package.

Q 13. What are the different types of interconnect technologies used in packaging?

Various interconnect technologies are used in semiconductor packaging, each with its own advantages and disadvantages:

- Wire Bonding: Small diameter gold or aluminum wires are thermo-sonically bonded between the die and the package leads. It’s a mature technology, cost-effective but limited in bandwidth and prone to fatigue.

- Flip-Chip Technology: The die is flipped over and directly bonded to the substrate using solder bumps. This provides higher interconnect density, shorter signal paths, and improved performance, but it’s more complex and costly.

- Tape Automated Bonding (TAB): Uses flexible printed circuits to interconnect the die to the package leads. It’s suitable for high-density interconnections and flexible substrates.

- Through-Silicon Vias (TSV): Vertical interconnects drilled through the silicon die, enabling 3D stacking of dies and increased integration density. It’s highly advanced, offering high bandwidth, but with higher manufacturing costs.

The choice of interconnect technology depends on factors such as performance requirements, cost, and manufacturing complexity.

Q 14. Describe the process of molding a semiconductor package.

Molding a semiconductor package typically involves encapsulating the die and its interconnections within a protective plastic compound (usually epoxy molding compound or EMC). This protects the internal components from environmental damage and mechanical stress.

- Die Preparation: The die is prepared and attached to a lead frame or substrate.

- Lead Frame Placement: The lead frame, which provides external connections, is positioned in a mold cavity.

- Transfer Molding: The EMC is transferred into the mold cavity, completely surrounding the die and lead frame.

- Curing: The mold is heated and cured under pressure to solidify the EMC.

- Demolding: The molded package is removed from the mold.

- Trimming and Finishing: Excess EMC is trimmed, and the leads are formed to meet specifications.

The molding process requires precise control of temperature, pressure, and time to ensure proper encapsulation and avoid defects like voids, cracks, or delamination.

Q 15. Explain the role of solder in semiconductor packaging.

Solder plays a crucial role in semiconductor packaging by providing the electrical and mechanical connection between the die (the semiconductor chip) and the package substrate, as well as between the package and the printed circuit board (PCB). Think of it as the glue and the electrical pathway that holds everything together.

Its primary functions include:

- Electrical Conductivity: Solder’s excellent electrical conductivity ensures a low-resistance path for signal transmission and power delivery.

- Mechanical Interconnection: It provides a strong, reliable mechanical bond that withstands thermal cycling (temperature fluctuations) and vibrations during operation.

- Thermal Management: Certain solder alloys facilitate heat dissipation from the die to the package and ultimately to the environment, preventing overheating.

Different types of solder are used depending on the application, with lead-free solders becoming increasingly prevalent due to environmental regulations. The choice of solder alloy influences the melting point, mechanical strength, and reliability of the connection.

For example, eutectic tin-lead (SnPb) solder was widely used for its excellent wetting characteristics, but its lead content led to its phase-out. Lead-free solders, such as tin-silver-copper (SnAgCu), are now commonly employed, though they often require more sophisticated reflow processes.

Career Expert Tips:

- Ace those interviews! Prepare effectively by reviewing the Top 50 Most Common Interview Questions on ResumeGemini.

- Navigate your job search with confidence! Explore a wide range of Career Tips on ResumeGemini. Learn about common challenges and recommendations to overcome them.

- Craft the perfect resume! Master the Art of Resume Writing with ResumeGemini’s guide. Showcase your unique qualifications and achievements effectively.

- Don’t miss out on holiday savings! Build your dream resume with ResumeGemini’s ATS optimized templates.

Q 16. What are the key considerations for selecting a suitable package for a specific application?

Selecting the right package is critical for the success of a semiconductor device. Several key factors must be considered, including:

- Device Functionality and Performance: The package must be able to support the device’s electrical characteristics, such as pin count, power consumption, and signal speed. A high-performance processor needs a package with excellent thermal management capabilities, while a low-power sensor might only require a simple package.

- Cost: Packaging contributes significantly to the overall cost. Choosing a simpler, less expensive package is important for cost-sensitive applications.

- Size and Weight: Miniaturization is vital in many applications like smartphones and wearables. Therefore, package size and weight are major constraints.

- Reliability: The package must ensure the long-term reliability of the device under various operating conditions, such as temperature variations, humidity, and mechanical stress. This involves considering factors like thermal cycling resistance and mechanical shock resistance.

- Thermal Management: Effective heat dissipation is crucial for preventing device failure. Package materials, design, and thermal vias significantly influence thermal performance. A package with insufficient thermal management can lead to performance degradation or early failure.

- Environmental Considerations: Compliance with environmental regulations (e.g., RoHS for lead-free solders) and material selection are essential.

Consider a high-end graphics processing unit (GPU): it will demand a large package with advanced thermal solutions like heat spreaders and heat pipes to manage its high power dissipation. In contrast, a simple temperature sensor may only need a tiny surface-mount package.

Q 17. How does the choice of packaging affect the overall system performance?

Packaging significantly affects overall system performance in several ways:

- Signal Integrity: The package’s design and materials influence signal quality, affecting speed, noise, and data transmission reliability. Poor package design can lead to signal attenuation, reflections, and crosstalk, especially at high frequencies.

- Power Delivery: The package’s power delivery network (PDN) impacts the device’s ability to operate efficiently. A poorly designed PDN can result in voltage drops and noise, affecting device stability and performance.

- Thermal Performance: Excessive heat generated by the die can cause performance degradation or failure if the package cannot effectively dissipate it. This is especially critical for high-power devices.

- Size and Weight: The package’s size and weight directly influence the size and weight of the overall system, affecting portability and form factor in applications such as portable electronics.

- Reliability: A reliable package ensures the long-term operational reliability of the entire system, reducing downtime and maintenance costs.

For instance, a poorly designed package with inadequate thermal management in a high-performance server could lead to overheating, system instability, and ultimately, costly downtime.

Q 18. Explain the impact of package design on signal integrity.

Package design significantly impacts signal integrity. High-speed signals are particularly susceptible to various parasitic effects introduced by the package. These effects can lead to signal degradation, noise, and crosstalk, ultimately compromising system performance.

Key considerations include:

- Trace Length and Width: Long and narrow traces can introduce significant inductance and capacitance, leading to signal distortion. Optimal trace dimensions are crucial for minimizing these effects.

- Dielectric Material: The dielectric material used in the package influences signal propagation delay and crosstalk. Low-permittivity materials are preferred for high-speed applications.

- Grounding and Shielding: Effective grounding and shielding techniques are vital to minimize noise and crosstalk. Careful design of ground planes and shield layers is essential.

- Via Placement and Size: Vias (interconnections between different layers) can introduce inductance and capacitance. Careful placement and appropriate sizing of vias are important to reduce these effects.

- Simulation and Modeling: Electromagnetic (EM) simulations are essential for predicting and mitigating signal integrity issues before manufacturing. Software tools like Ansys HFSS or CST Microwave Studio are often used.

For instance, in high-speed data communication, even a small amount of signal degradation can lead to bit errors, data loss, and system malfunctions. Therefore, meticulous package design and advanced simulation are vital for ensuring robust signal integrity.

Q 19. Describe the different types of testing performed on semiconductor packages (e.g., electrical, mechanical, environmental).

Semiconductor packages undergo rigorous testing to ensure their quality and reliability. These tests can be broadly classified as:

- Electrical Tests: These assess the electrical characteristics of the package, such as resistance, capacitance, inductance, signal integrity, and power delivery capabilities. Automated test equipment (ATE) is commonly used for high-throughput electrical testing.

- Mechanical Tests: These evaluate the package’s ability to withstand mechanical stress and shocks during handling, transportation, and operation. Tests include temperature cycling, thermal shock, vibration, and drop testing.

- Environmental Tests: These assess the package’s performance under various environmental conditions, such as humidity, temperature extremes, and pressure. These tests ensure the package’s ability to withstand harsh operating conditions.

- Reliability Tests: These are long-term tests designed to evaluate the package’s durability and reliability under accelerated stress conditions. Examples include highly accelerated life testing (HALT) and highly accelerated stress screening (HASS).

For example, a package intended for automotive applications will require extensive vibration and temperature cycling tests to meet the stringent reliability requirements of the automotive industry. Similarly, a package for aerospace applications would undergo more stringent environmental testing to ensure its ability to function in extreme conditions.

Q 20. What are some common industry standards related to semiconductor packaging?

Several industry standards govern semiconductor packaging, ensuring interoperability and quality. Some prominent ones include:

- JEDEC (Joint Electron Device Engineering Council): JEDEC develops standards for various aspects of semiconductor packaging, including package dimensions, materials, testing methods, and reliability requirements. Many JEDEC standards are widely adopted by the industry.

- IPC (Institute for Printed Circuits): IPC provides standards for printed circuit board (PCB) design, fabrication, and assembly, which are closely related to semiconductor packaging.

- EIA (Electronic Industries Alliance): EIA contributes to various electronic industry standards, some of which impact semiconductor packaging.

- ISO (International Organization for Standardization): ISO provides international standards related to quality management, environmental management, and other areas that impact semiconductor packaging.

Adherence to these standards ensures that packages meet specified performance requirements, promote interoperability, and maintain consistent quality across different manufacturers. For example, JEDEC standards define specific package outlines and pin configurations for various package types, which simplifies design and manufacturing.

Q 21. Explain the concept of package level testing (PLT) and its benefits.

Package Level Testing (PLT) is a critical stage in semiconductor manufacturing where the assembled package is tested before it’s integrated into the final product. It’s done after the die is packaged, but before it’s mounted onto a PCB.

Benefits of PLT include:

- Early Defect Detection: PLT allows for the identification and removal of defective packages early in the manufacturing process, reducing scrap and rework costs. This is more cost-effective than discovering failures after PCB assembly.

- Improved Yield: By identifying and removing defective packages before PCB assembly, PLT helps increase the overall yield of the final product.

- Enhanced Reliability: PLT ensures that only high-quality packages are used in the final product, thereby enhancing the overall reliability and longevity of the system.

- Simplified Debugging: If a problem is discovered in the final product, PLT can help isolate the issue to a defective package, simplifying troubleshooting and debugging.

Imagine a situation where a defective package escapes PLT. This defect would then propagate to the PCB assembly level, potentially causing widespread failure across a large number of finished products, resulting in significant time, cost and reputation damage. PLT prevents this scenario from happening.

Q 22. How does power consumption influence package design?

Power consumption is a paramount concern in semiconductor packaging, significantly influencing design choices at every stage. Higher power densities necessitate effective thermal management to prevent overheating and device failure. This translates into several key design considerations:

- Package Material Selection: Materials with high thermal conductivity, like copper or diamond substrates, are preferred for efficient heat dissipation. For example, using a copper-based heat spreader beneath the die significantly improves thermal performance compared to using a plastic substrate.

- Thermal Vias: These vertical conductive pathways within the package facilitate heat transfer from the die to the heat sink. The number, size, and placement of thermal vias are optimized to maximize heat removal.

- Heat Sink Design: The heat sink’s size, material, and surface area directly impact its effectiveness. Sophisticated heat sinks incorporating microchannels or fins are often used for high-power applications. Fin height, spacing and fin density are carefully considered.

- Packaging Technique: Packaging methods such as flip-chip or system-in-package (SiP) offer improved thermal performance compared to wire-bonded packages by shortening the thermal path.

- Power Delivery Network (PDN): A well-designed PDN minimizes voltage drop and reduces power loss, which in turn reduces heat generation. This involves careful routing of power traces and the use of appropriate decoupling capacitors.

Ignoring power consumption during package design can lead to premature failure, reduced performance, and ultimately, product recalls. Therefore, thermal analysis and simulation are critical steps throughout the design process.

Q 23. What are the current trends and future directions in semiconductor packaging?

Semiconductor packaging is undergoing a rapid evolution driven by the relentless demand for higher performance, smaller form factors, and reduced power consumption. Here are some prominent trends and future directions:

- 3D Packaging: Stacking multiple dies vertically allows for increased functionality and higher density integration. Through-silicon vias (TSVs) are crucial for enabling this vertical interconnect.

- Advanced Substrate Technologies: The use of high-performance substrates such as silicon interposers or organic substrates with embedded passives is becoming increasingly prevalent to improve signal integrity and reduce parasitic effects.

- Heterogeneous Integration: Combining different types of dies, such as memory, processors, and sensors, within a single package enables the creation of highly functional and efficient systems.

- Advanced Packaging Techniques: Techniques like fan-out wafer-level packaging (FOWLP) offer increased I/O density and smaller form factors, benefiting applications like mobile devices and high-speed data centers.

- Embedded Components: Integrating passive components like resistors and capacitors directly into the package reduces footprint and improves performance by reducing parasitic inductance and capacitance.

- AI-driven Design Automation: Artificial intelligence is being employed to optimize package designs, predicting performance, and improving yield.

The future of semiconductor packaging is inextricably linked with the broader advancements in electronics. The focus will be on creating ever more powerful, efficient, and miniaturized devices, demanding ever more sophisticated packaging solutions.

Q 24. Describe your experience with specific packaging technologies (e.g., 3D packaging, PoP, WLCSP).

My experience spans various packaging technologies, each with its unique strengths and challenges.

- 3D Packaging: I’ve been involved in several projects utilizing through-silicon vias (TSVs) for 3D stacking. This involved detailed analysis of TSV density, aspect ratio, and reliability concerns. We optimized the design to minimize void formation during TSV fabrication and ensured signal integrity across the stacked dies. A key challenge was managing the warpage and stress induced by the stacking process.

- Package on Package (PoP): I’ve worked extensively with PoP designs, integrating memory chips directly onto the processor package. This required careful consideration of the thermal management and alignment precision to ensure reliable interconnection. Careful attention was paid to the solder bumps used for interconnection and the mechanical stress associated with the assembly process.

- Wafer-Level Chip Scale Package (WLCSP): In several projects I’ve designed and implemented WLCSP packages, focusing on miniaturization and cost reduction. This involved careful selection of underfill materials to ensure device protection and improved reliability. Challenges here included managing warpage during the molding process and achieving high-yield assembly.

In each case, the focus was on balancing performance, cost, and reliability requirements. Rigorous simulation and testing were crucial for ensuring product success.

Q 25. Explain your understanding of different substrate materials and their properties.

Substrate materials play a critical role in semiconductor packaging, influencing performance, cost, and reliability. The choice of material depends on the specific application requirements.

- Silicon: Offers excellent electrical and thermal conductivity, making it ideal for high-performance applications. However, it is expensive and brittle.

- Organic Substrates (e.g., BT, PI): Cost-effective and flexible, often used for low-cost applications and flexible electronics. They generally have lower thermal conductivity than silicon.

- Ceramic (e.g., Alumina, Aluminum Nitride): Offers high thermal conductivity and good mechanical strength, suitable for high-power applications. They can be more expensive than organic substrates.

- Copper: Excellent thermal conductor, often used as heat spreaders in packages to improve heat dissipation. It can be challenging to integrate with other materials.

- Liquid Crystal Polymer (LCP): A relatively new material, offering high temperature resistance and low dielectric constant, ideal for high-frequency applications.

Understanding the thermal and mechanical properties, as well as the dielectric constant and coefficient of thermal expansion (CTE) of these materials is critical for successful package design. Mismatch in CTE between different materials can lead to stress and cracking during thermal cycling.

Q 26. How do you manage conflicts between design requirements and manufacturing constraints in semiconductor packaging?

Managing conflicts between design requirements and manufacturing constraints is a constant challenge in semiconductor packaging. A structured approach is crucial for successful product development.

- Early Collaboration: Engaging design and manufacturing engineers early in the design process facilitates the identification and resolution of potential conflicts before significant investments are made.

- Design for Manufacturing (DFM): Adopting DFM principles during the design phase ensures that the package is manufacturable with existing equipment and processes. This might involve simplifying the design, using readily available components, and avoiding complex assembly steps.

- Tolerance Analysis: Conducting tolerance analysis helps determine the impact of manufacturing variations on package performance and reliability. This identifies critical parameters that require tighter control during manufacturing.

- Iterative Design Process: Using an iterative design process, with frequent communication between design and manufacturing teams, allows for early detection and resolution of potential issues.

- Process Capability Studies: Conducting process capability studies to verify that manufacturing processes meet the required specifications.

A successful approach involves a balance between performance optimization and manufacturing feasibility. Sometimes, minor design compromises are necessary to ensure manufacturability and reduce costs without sacrificing critical performance aspects.

Q 27. Describe your experience with Design of Experiments (DOE) in the context of semiconductor packaging.

Design of Experiments (DOE) is an indispensable tool in semiconductor packaging for optimizing package design and identifying critical parameters influencing performance and yield.

In my experience, we’ve utilized DOE methodologies extensively for several projects. For instance, we used a Taguchi method to optimize the underfill process in a WLCSP package. By carefully selecting factors like underfill viscosity, curing temperature, and pressure, we were able to minimize voids and improve yield significantly. A full factorial DOE would have been far too resource intensive, so the Taguchi method was a sensible and efficient alternative.

Another example involved using a fractional factorial DOE to study the influence of various package parameters on the thermal performance of a high-power package. This allowed us to identify the most influential factors and optimize the design for better heat dissipation.

DOE helps to:

- Reduce the number of experiments required to study complex systems.

- Identify the most significant factors impacting performance and yield.

- Quantify the impact of each factor on the response variables.

- Optimize process parameters and reduce variability.

Through the effective application of DOE, we have significantly improved package performance, reduced development costs, and accelerated time to market.

Q 28. What are your thoughts on the future of semiconductor packaging and its role in the continued advancement of electronics?

The future of semiconductor packaging is bright, and its role in enabling advancements in electronics is pivotal. We’ll see continued advancements in several key areas:

- Increased Integration: Packages will continue to integrate more functionality, combining diverse components within increasingly smaller spaces. This requires innovative interconnect technologies and advanced materials.

- Improved Performance: Packaging technologies will need to address the increasing power consumption and signal integrity challenges associated with higher-frequency components and advanced nodes.

- Sustainability: More environmentally friendly materials and manufacturing processes will be essential as the industry strives for greater sustainability.

- Artificial Intelligence: AI and machine learning will play a larger role in design, optimization, and manufacturing, leading to more efficient and effective package development.

- Miniaturization: The relentless pursuit of miniaturization will drive the development of ever-smaller and more densely packed packages.

In summary, semiconductor packaging is not merely a supporting technology; it is an integral driver of innovation in the electronics industry. Its future advancements will determine the capabilities and limitations of future electronics, from smartphones to high-performance computing systems.

Key Topics to Learn for Semiconductor Packaging Interview

- Package Types & Technologies: Understand the differences and applications of various packaging types (e.g., wire bonding, flip-chip, system-in-package (SiP), 3D packaging). Explore the trade-offs between cost, performance, and size for each.

- Materials Science: Gain a strong grasp of the materials used in semiconductor packaging (e.g., underfills, molding compounds, substrates). Understand their properties and how they impact package reliability and performance.

- Thermal Management: Learn about heat dissipation techniques in semiconductor packages and the importance of thermal design for reliability. Be prepared to discuss various heat sink solutions and their effectiveness.

- Reliability & Failure Analysis: Familiarize yourself with common failure mechanisms in semiconductor packages and the methods used to analyze and prevent them. This includes understanding stress, fatigue, and environmental effects.

- Manufacturing Processes: Understand the key steps involved in semiconductor packaging manufacturing, including die attach, wire bonding, molding, and testing. Be able to discuss process optimization and yield improvement strategies.

- Electrical Testing & Characterization: Learn about various electrical testing methods used to characterize the performance of semiconductor packages. Understand concepts like signal integrity, power integrity, and electromagnetic interference (EMI).

- Advanced Packaging Techniques: Explore emerging trends in semiconductor packaging, such as heterogeneous integration, advanced interconnect technologies, and miniaturization techniques. Discuss their potential impact on future device designs.

Next Steps

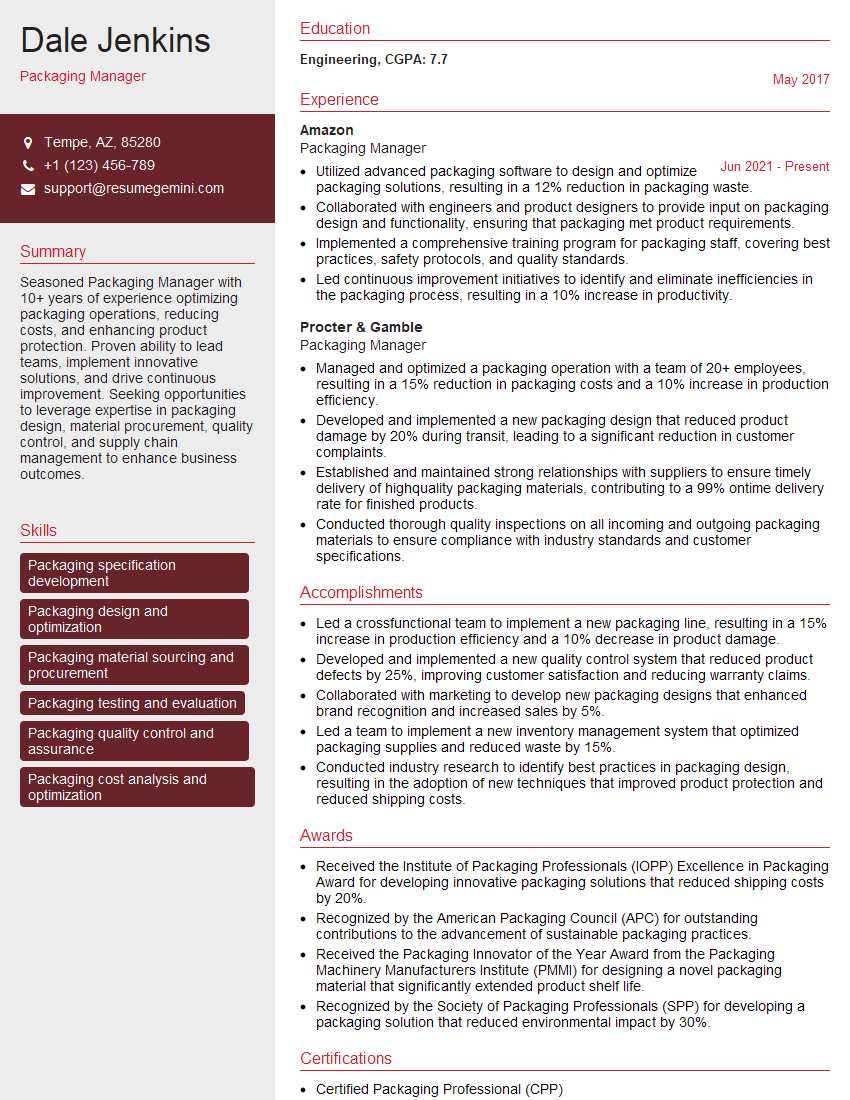

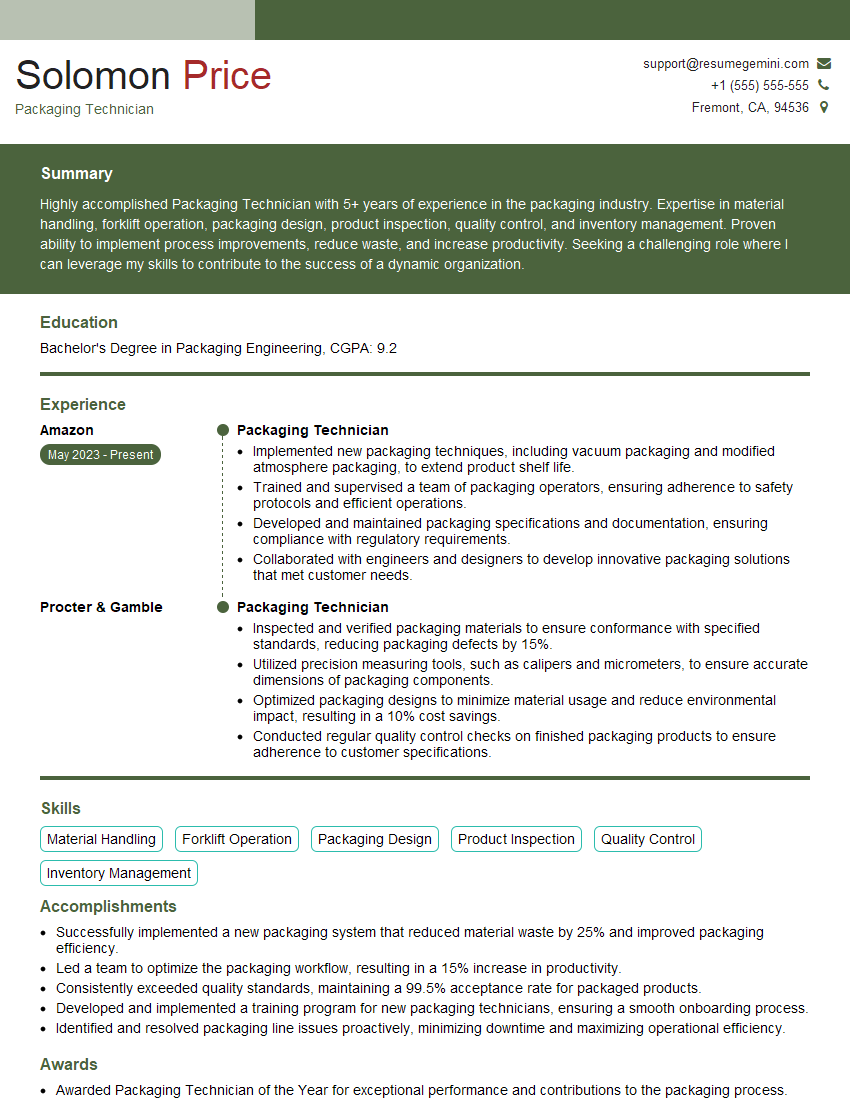

Mastering semiconductor packaging opens doors to exciting and rewarding career opportunities in a rapidly evolving industry. To maximize your job prospects, it’s crucial to present your skills effectively. Crafting an ATS-friendly resume is key to getting your application noticed by recruiters. We highly recommend using ResumeGemini to build a professional and impactful resume that highlights your expertise. ResumeGemini offers a streamlined process and provides examples of resumes tailored specifically to the Semiconductor Packaging field, helping you stand out from the competition.

Explore more articles

Users Rating of Our Blogs

Share Your Experience

We value your feedback! Please rate our content and share your thoughts (optional).

What Readers Say About Our Blog

Attention music lovers!

Wow, All the best Sax Summer music !!!

Spotify: https://open.spotify.com/artist/6ShcdIT7rPVVaFEpgZQbUk

Apple Music: https://music.apple.com/fr/artist/jimmy-sax-black/1530501936

YouTube: https://music.youtube.com/browse/VLOLAK5uy_noClmC7abM6YpZsnySxRqt3LoalPf88No

Other Platforms and Free Downloads : https://fanlink.tv/jimmysaxblack

on google : https://www.google.com/search?q=22+AND+22+AND+22

on ChatGPT : https://chat.openai.com?q=who20jlJimmy20Black20Sax20Producer

Get back into the groove with Jimmy sax Black

Best regards,

Jimmy sax Black

www.jimmysaxblack.com

Hi I am a troller at The aquatic interview center and I suddenly went so fast in Roblox and it was gone when I reset.

Hi,

Business owners spend hours every week worrying about their website—or avoiding it because it feels overwhelming.

We’d like to take that off your plate:

$69/month. Everything handled.

Our team will:

Design a custom website—or completely overhaul your current one

Take care of hosting as an option

Handle edits and improvements—up to 60 minutes of work included every month

No setup fees, no annual commitments. Just a site that makes a strong first impression.

Find out if it’s right for you:

https://websolutionsgenius.com/awardwinningwebsites

Hello,

we currently offer a complimentary backlink and URL indexing test for search engine optimization professionals.

You can get complimentary indexing credits to test how link discovery works in practice.

No credit card is required and there is no recurring fee.

You can find details here:

https://wikipedia-backlinks.com/indexing/

Regards

NICE RESPONSE TO Q & A

hi

The aim of this message is regarding an unclaimed deposit of a deceased nationale that bears the same name as you. You are not relate to him as there are millions of people answering the names across around the world. But i will use my position to influence the release of the deposit to you for our mutual benefit.

Respond for full details and how to claim the deposit. This is 100% risk free. Send hello to my email id: [email protected]

Luka Chachibaialuka

Hey interviewgemini.com, just wanted to follow up on my last email.

We just launched Call the Monster, an parenting app that lets you summon friendly ‘monsters’ kids actually listen to.

We’re also running a giveaway for everyone who downloads the app. Since it’s brand new, there aren’t many users yet, which means you’ve got a much better chance of winning some great prizes.

You can check it out here: https://bit.ly/callamonsterapp

Or follow us on Instagram: https://www.instagram.com/callamonsterapp

Thanks,

Ryan

CEO – Call the Monster App

Hey interviewgemini.com, I saw your website and love your approach.

I just want this to look like spam email, but want to share something important to you. We just launched Call the Monster, a parenting app that lets you summon friendly ‘monsters’ kids actually listen to.

Parents are loving it for calming chaos before bedtime. Thought you might want to try it: https://bit.ly/callamonsterapp or just follow our fun monster lore on Instagram: https://www.instagram.com/callamonsterapp

Thanks,

Ryan

CEO – Call A Monster APP

To the interviewgemini.com Owner.

Dear interviewgemini.com Webmaster!

Hi interviewgemini.com Webmaster!

Dear interviewgemini.com Webmaster!

excellent

Hello,

We found issues with your domain’s email setup that may be sending your messages to spam or blocking them completely. InboxShield Mini shows you how to fix it in minutes — no tech skills required.

Scan your domain now for details: https://inboxshield-mini.com/

— Adam @ InboxShield Mini

Reply STOP to unsubscribe

Hi, are you owner of interviewgemini.com? What if I told you I could help you find extra time in your schedule, reconnect with leads you didn’t even realize you missed, and bring in more “I want to work with you” conversations, without increasing your ad spend or hiring a full-time employee?

All with a flexible, budget-friendly service that could easily pay for itself. Sounds good?

Would it be nice to jump on a quick 10-minute call so I can show you exactly how we make this work?

Best,

Hapei

Marketing Director

Hey, I know you’re the owner of interviewgemini.com. I’ll be quick.

Fundraising for your business is tough and time-consuming. We make it easier by guaranteeing two private investor meetings each month, for six months. No demos, no pitch events – just direct introductions to active investors matched to your startup.

If youR17;re raising, this could help you build real momentum. Want me to send more info?

Hi, I represent an SEO company that specialises in getting you AI citations and higher rankings on Google. I’d like to offer you a 100% free SEO audit for your website. Would you be interested?

Hi, I represent an SEO company that specialises in getting you AI citations and higher rankings on Google. I’d like to offer you a 100% free SEO audit for your website. Would you be interested?