Cracking a skill-specific interview, like one for VHDL and Verilog for FPGA Programming, requires understanding the nuances of the role. In this blog, we present the questions you’re most likely to encounter, along with insights into how to answer them effectively. Let’s ensure you’re ready to make a strong impression.

Questions Asked in VHDL and Verilog for FPGA Programming Interview

Q 1. Explain the difference between VHDL and Verilog.

VHDL (VHSIC Hardware Description Language) and Verilog are both Hardware Description Languages (HDLs) used to design and model digital circuits, primarily for FPGAs and ASICs. However, they differ significantly in their syntax, style, and features. Think of it like choosing between two different programming languages – both accomplish the same goal, but with distinct approaches.

- Syntax: VHDL is strongly typed and uses a more formal, Ada-like syntax with explicit declarations. Verilog, on the other hand, is less strict, resembling C in its syntax, with implicit declarations often possible. This makes Verilog often perceived as more intuitive for programmers familiar with C-like languages, whereas VHDL is more suitable for larger, more complex projects where strong typing and design structure are paramount.

- Design Methodology: VHDL often favors a more structured, top-down design approach, with clear separation of modules and well-defined interfaces. Verilog allows for a more flexible, bottom-up design, where smaller modules can be built and combined easily. The choice depends on the project’s complexity and the team’s preferred design style.

- Data Types: VHDL has a richer set of built-in data types, allowing for more precise modeling of different signal types. Verilog has fewer built-in types, but provides flexibility through user-defined types. This difference often influences the readability and maintainability of the code.

- Concurrency Modeling: Both languages handle concurrency, but in different ways. VHDL uses processes and signals, whereas Verilog utilizes always blocks and the concepts of blocking and non-blocking assignments (explained further in the next question).

In practice, the best choice depends on project requirements, team expertise, and personal preferences. Large projects often benefit from VHDL’s rigor, while smaller projects may find Verilog’s simpler syntax more efficient.

Q 2. What are the key differences between blocking and non-blocking assignments in Verilog?

Blocking and non-blocking assignments are crucial concepts in Verilog, especially within always blocks, which define concurrent processes. They determine the order in which variable assignments are executed within a single time step of a simulation.

- Blocking Assignments (

=): Blocking assignments execute sequentially. The right-hand side is evaluated and assigned to the left-hand side *before* the next statement is executed. Imagine it like a single-lane road; one car (assignment) must finish before the next one can start. - Non-blocking Assignments (

<=): Non-blocking assignments evaluate all the right-hand sides *before* any assignments occur. The assignments take place concurrently at the end of the time step. It's like a multi-lane highway where all cars start at once, but each car reaches its destination concurrently.

Here's an example illustrating the difference:

module blocking_nonblocking;

reg a, b, c, d;

always @(posedge clk) begin

a = b; // Blocking

c <= d; // Non-blocking

end

endmodule

In the blocking assignment, a gets the value of b *immediately*, before the next statement executes. In the non-blocking assignment, both the values of d (for assigning to c) are evaluated, then the values of c and a are scheduled for update, *simultaneously*, at the end of the time step. This difference significantly impacts simulation results, especially in concurrent scenarios. Blocking assignments are typically used for sequential operations, while non-blocking assignments are commonly used in modeling hardware concurrency.

Q 3. Describe the process of synthesizing VHDL code for an FPGA.

Synthesizing VHDL code for an FPGA transforms the abstract HDL description into a netlist – a description of the hardware connections required to implement the design on the target FPGA. It's like translating a recipe (VHDL code) into a detailed assembly plan (netlist) for building a cake (circuit) in a specific kitchen (FPGA).

- Design Entry: You write your VHDL code, defining modules, entities, and architectures to describe the desired functionality.

- Synthesis: A synthesis tool (e.g., Xilinx Vivado, Intel Quartus Prime) takes your VHDL code as input and analyzes it according to the target FPGA's architecture and constraints. It optimizes the design for area, speed, and power efficiency, creating an optimized netlist representation.

- Implementation: The synthesis tool's output (netlist) is then processed by the implementation tools. This stage involves place and route, which maps the logical elements in the netlist to specific physical resources (like look-up tables (LUTs) and flip-flops) on the FPGA and determines the routing of signals between them.

- Bitstream Generation: The final stage is generating the bitstream, a configuration file that contains the exact configuration data needed to load the design into the FPGA. The bitstream contains the programming details for all the physical resources.

- Verification: Through simulation and testing, you verify the correctness of the implemented design. This ensures that the synthesized hardware behaves as intended.

Synthesis involves many trade-offs between area, speed, and power. Different synthesis strategies and optimization settings can significantly influence the final outcome. For example, one might prioritize speed by allowing more resources to be used, while another approach would focus on optimizing area to minimize cost.

Q 4. How do you handle timing constraints in FPGA design?

Timing constraints are crucial in FPGA design because they define the timing requirements of your design. Meeting these constraints ensures your design operates correctly at the desired frequency and avoids timing violations. Think of timing constraints as the recipe's baking time – if not followed precisely, the cake might be burnt or undercooked.

Timing constraints are specified using a Constraint Description Language (typically SDC – Synopsys Design Constraints). Key elements include:

- Clock Constraints: Define the frequency and characteristics of the clock signals. This is critical for proper operation of synchronous elements.

- Input/Output Delays: Specify the delays associated with input and output signals, considering the physical characteristics of the connections.

- Setup and Hold Times: Define the minimum time a data signal must be stable before and after a clock edge for reliable data capture by flip-flops.

- False Paths: Specify signals that are not part of the critical timing path, allowing the synthesis and timing analysis tools to ignore them to improve optimization.

Timing analysis tools then verify the design's timing performance against these constraints. If violations occur, you need to optimize the design, using techniques like pipelining, re-timing, or choosing faster FPGA resources, to meet timing requirements. Ignoring timing constraints can lead to incorrect functionality or unpredictable behavior.

Q 5. Explain different types of FPGA architectures (e.g., LUT, DSP slices).

FPGAs are built using various fundamental building blocks, each contributing to the overall functionality and performance of the device. Consider these as the different ingredients that make up a cake.

- Look-Up Tables (LUTs): These are small memory elements that implement combinational logic functions. Imagine them as small calculators; you input a combination of bits, and they output a pre-programmed result. They are fundamental components that build more complex logic.

- Flip-Flops (FFs): These are sequential elements that store data and are clocked. They are essential for storing state and building registers, counters, and other state machines. They are the cake's 'memory' elements.

- DSP Slices: These are specialized blocks designed for implementing arithmetic functions, particularly those involving multiplication and accumulation. They are optimized for high performance in tasks such as signal processing. They are the cake's 'specialized baking tools'.

- Block RAM (BRAM): These are larger memory blocks providing more significant storage capacity compared to individual flip-flops. Useful for implementing large memories, buffers, and FIFOs. This is where the bigger ingredients for the cake are stored.

- Hardened Processors (e.g., ARM processors): Some FPGAs include integrated, hardened processors for running software alongside the FPGA's hardware logic. This allows for a mixed software/hardware approach to design. This is the oven itself, where the cake is baked.

Different FPGA architectures vary in the number and arrangement of these resources, influencing the performance and capabilities of the device. Understanding the architecture of your target FPGA is essential for optimal design.

Q 6. What are the various levels of abstraction in HDL design?

HDL design employs various levels of abstraction, offering different levels of detail and control over the design process. This is analogous to building a house: you start with the blueprint (high-level), then build the walls and rooms (medium-level), finally wiring electricity and plumbing (low-level).

- Behavioral Level: This is the highest level of abstraction, focusing on the desired functionality without specifying the implementation details. You describe what the circuit should do, not how it should do it. This is like creating the overall structure and rooms.

- Register-Transfer Level (RTL): This intermediate level describes the data flow between registers and functional units. You define the registers, the operations performed on the data, and the sequencing of operations. This is similar to building walls and defining the interior of the house.

- Gate Level: This is the lowest level of abstraction, specifying the design using logic gates (AND, OR, XOR, etc.). It directly maps to the physical components of the FPGA. This is analogous to wiring up all the electricity and plumbing in the house.

Choosing the appropriate level of abstraction depends on the design's complexity, the designer's skill, and the tools used. Behavioral modeling allows for rapid prototyping and easy modification, while gate-level design provides maximum control but requires more effort and expertise. RTL is a sweet spot, balancing abstraction and control, and is most commonly used for FPGA design.

Q 7. Describe your experience with different FPGA vendors (e.g., Xilinx, Altera/Intel).

I have extensive experience with both Xilinx and Altera (now Intel) FPGAs, having worked on various projects using their respective tools and devices. My experience spans across different FPGA families, including Xilinx Virtex, Kintex, Artix, and UltraScale, and Intel Cyclone, Stratix, and MAX devices. My familiarity extends beyond just the hardware to encompass their respective design flows and toolsets.

- Xilinx Vivado: I'm proficient in using Vivado for synthesis, implementation, and bitstream generation. I've utilized its advanced features for timing closure, power optimization, and design analysis. I have also used their IP cores extensively in my projects.

- Intel Quartus Prime: Similarly, I have experience with Quartus Prime, utilizing its synthesis, implementation, and device programming capabilities. I'm familiar with Intel's IP catalog and have used their tools for various projects.

My experience with these vendors extends beyond simple design implementation to include debugging, performance optimization, and working with various constraints. I've consistently delivered high-quality, optimized designs that meet stringent performance requirements. I am also comfortable with the use of their respective constraint languages and have a deep understanding of their architectural nuances.

For instance, in one project using Xilinx UltraScale+, I leveraged the advanced features of the device, along with Vivado's advanced analysis tools, to optimize the power consumption while achieving challenging timing requirements. In another project with Intel Stratix, I utilized specific IP cores to accelerate certain processes and reduced design time significantly.

Q 8. How do you perform static timing analysis?

Static Timing Analysis (STA) is a crucial step in FPGA design verification. It analyzes the timing characteristics of a design to ensure it meets its performance requirements. Essentially, it checks if signals can propagate through the circuit within the specified timing constraints, identifying potential timing violations like setup and hold violations.

The process typically involves:

- Reading the design netlist: The STA tool reads the netlist, a description of the interconnected components in the design, generated by the synthesis tool.

- Extracting timing information: The tool extracts timing information from the netlist and the target FPGA's technology library (containing delay information for each component).

- Analyzing paths: The tool analyzes all possible signal paths in the design, calculating the delay along each path.

- Comparing to constraints: The calculated delays are then compared against the timing constraints specified by the designer (e.g., clock frequency, setup/hold times). Violations are reported if a path's delay exceeds the constraint.

- Reporting violations: The tool generates a report that highlights any timing violations, including the affected paths, the severity of the violation, and suggestions for mitigation.

Example: Imagine a design with a clock frequency of 100MHz. STA would check if any signal path from one flip-flop to another takes longer than 10ns (1/100MHz). If a path takes 12ns, a setup time violation is reported, indicating that the data might not be properly captured by the receiving flip-flop.

In my experience, effective STA requires careful constraint definition, thorough understanding of the target FPGA architecture, and iterative design refinement to resolve violations. Understanding the trade-offs between area, performance and power is crucial in navigating STA challenges.

Q 9. What are metastability and how to mitigate it?

Metastability is a phenomenon that occurs in flip-flops and latches when their inputs change very close to the clock edge. Instead of settling to a stable '0' or '1', the output enters an unpredictable state that can persist for an indeterminate time. This unstable state can propagate through the design, leading to unpredictable behavior and system failures.

Think of it like a coin spinning in the air—it's neither heads nor tails until it lands. In metastability, the flip-flop's output is neither a '0' nor a '1' until it eventually settles (potentially after a long and unpredictable time).

Mitigation Techniques:

- Synchronization Stages: The most common mitigation technique involves using multiple flip-flops in series. Each subsequent flip-flop has a higher probability of settling to a stable state. The more stages you add, the lower the probability of metastability propagating.

- Asynchronous FIFO: For high-speed asynchronous data transfers, asynchronous FIFOs are designed to handle metastability gracefully. They often employ robust synchronization techniques and error detection mechanisms.

- Careful Clocking: Proper clock distribution and management is essential to minimize the chances of metastability. Avoiding clock skew and ensuring sufficient clock-to-out delays helps.

- Proper Signal Integrity: Maintaining signal integrity is important to avoid signals being corrupted near the clock edge, which can increase metastability risk.

Example: If a signal from an external asynchronous source needs to be registered in your FPGA, a two-stage synchronizer (two flip-flops in series) is usually implemented to reduce the probability of metastability propagating further into the design. It's important to note that metastability cannot be completely eliminated, but its probability can be drastically reduced.

Q 10. Explain different types of testbenches (e.g., behavioral, structural).

Testbenches are crucial for verifying the functionality of HDL code. They simulate the design's behavior by providing stimuli and checking the outputs. There are several types, each with its strengths and weaknesses:

- Behavioral Testbenches: These testbenches describe the test stimuli and expected behavior using HDL code at a high level of abstraction. They don't model the exact structure of the design but rather focus on its functional behavior. This approach is efficient for early verification stages but might not catch all structural errors.

- Structural Testbenches: These testbenches instantiate the design under test (DUT) as a component and drive it with stimuli at its ports. They are more detailed than behavioral testbenches and often used for lower-level verification, closer to the hardware's actual structure. They are good for testing interaction between components but can be more complex to develop.

- Mixed Testbenches: A combination of behavioral and structural approaches. Often, a high-level behavioral model is used for initial checks, then transitioned to structural tests for more rigorous verification.

- Transaction-Level Modeling (TLM): TLM uses higher-level abstractions that represent interactions between blocks at a more functional level, thereby simplifying simulation and increasing verification speed.

Example (Behavioral): A behavioral testbench for a simple adder might generate random input values and compare the DUT's output with the expected sum. A structural testbench would directly connect the adder to the input and output signals and check the outputs.

In my experience, a hybrid approach, starting with behavioral and moving towards structural verification as needed, is most effective for comprehensive testing.

Q 11. How do you debug VHDL or Verilog code?

Debugging VHDL or Verilog code involves systematically identifying and correcting errors. The process typically involves:

- Simulation: Running the design in a simulator with appropriate testbenches to observe its behavior. This allows one to inspect signals, analyze timing, and track down logical errors.

- Waveform Viewing: Using waveform viewers to visualize signals over time. This helps identify timing issues, glitches, and unexpected signal values.

- Assertions and Coverage: Using assertions to check for expected conditions and coverage metrics to measure the completeness of verification.

- Formal Verification (advanced): Employing formal methods to prove or disprove properties of the design mathematically. This technique helps find subtle bugs that simulation might miss.

- Code Review: Having colleagues review the code to identify potential errors and improve code quality. A fresh pair of eyes can often spot things the original author missed.

- Debugging Tools in the Simulator: Most simulators offer built-in debugging features like breakpoints, stepping through the code, and signal monitoring which allows inspection of variables at runtime and can help pinpointing the root cause of a bug.

Example: If a signal is not behaving as expected, waveform viewing can reveal if it is receiving the correct inputs, and whether it's getting corrupted along the way. Breakpoints in the simulator can help pinpoint the line of code causing the issue.

Effective debugging often involves a combination of these techniques, requiring patience and a methodical approach.

Q 12. What are your experiences with version control systems for HDL code?

Version control systems (VCS) are absolutely essential for managing HDL code, particularly in collaborative projects. I have extensive experience with Git, which provides excellent features for tracking changes, collaborating with team members, and managing different versions of the code.

Using Git, I routinely branch for new features or bug fixes, commit code regularly with clear and concise messages, and merge branches using proper merge strategies. This workflow allows for easy tracking of changes, rollback capabilities if needed, and conflict resolution.

In addition to Git, I've also worked with SVN in the past, but I find Git's distributed nature to be more flexible and efficient for HDL development, especially when dealing with large projects and multiple collaborators.

I understand the importance of clear commit messages and following a structured branching strategy to ensure traceability and maintainability of the codebase. My experience working with VCS helps in avoiding confusion and conflicts between different versions and keeps a complete history of the design’s evolution.

Q 13. Describe your experience with various synthesis tools.

My experience with synthesis tools includes extensive use of Synopsys Design Compiler and Xilinx Vivado. I’m also familiar with Intel Quartus Prime. Each tool has its strengths and nuances.

Synopsys Design Compiler offers a robust scripting interface and advanced optimization capabilities, making it suitable for large and complex designs. I've utilized its various optimization options, including timing optimization, area optimization, and power optimization, to meet specific design requirements.

Xilinx Vivado offers a comprehensive suite of tools that are tightly integrated with the Xilinx FPGA architecture. Its constraints management and design analysis features are powerful, and its built-in synthesis engine works very well for Xilinx FPGAs. I've extensively used Vivado's IP integrator for creating and integrating complex design blocks.

Intel Quartus Prime is a strong contender, especially for Intel FPGAs. Its ease of use and integration with the Intel tools make it a good option for simpler to medium complexity projects.

I understand how synthesis tool options affect resource utilization, timing performance and power consumption, and can effectively choose appropriate settings and constraints for various designs and optimization targets. Understanding the intricacies of each tool is essential for achieving optimal results in terms of performance, area and power efficiency.

Q 14. What are your experiences with different simulation tools?

My experience encompasses several simulation tools, predominantly ModelSim and Vivado Simulator (integrated within Xilinx Vivado). I’ve also used ISim (for simpler designs and quicker turnaround) and VCS in the past.

ModelSim is a highly capable simulator with a powerful debugging environment. I've used it extensively for simulating designs of varying complexity, making use of its advanced features like functional coverage, code coverage, and debugging capabilities.

Vivado Simulator is well-integrated with the Vivado design flow and offers convenient debugging features that make it a natural choice for projects targeted at Xilinx FPGAs. It offers fast simulation for smaller projects and is very efficient when used with Xilinx IPs.

ISim is a fast simulator suitable for smaller projects where quick turnaround is more important than advanced features.

VCS is a highly performant simulator often used in larger industry projects where speed and verification throughput are critical, but it comes with a higher cost and steeper learning curve.

My selection of simulation tool depends on the project size, complexity, timing constraints, and the need for advanced features. I'm comfortable using a range of simulators to suit the project's needs, and I’m proficient in generating testbenches and running simulations, interpreting results, and using the debugging capabilities offered by these tools.

Q 15. Explain the concept of clock domain crossing.

Clock domain crossing (CDC) occurs when signals are transferred between different clock domains in an FPGA design. Each domain operates independently, with its own clock signal, potentially at different frequencies or phases. This creates challenges because a signal's state in one domain might be misinterpreted in another, leading to metastability issues – an unpredictable state where the receiving flip-flop can't settle to a definitive 0 or 1.

Imagine two synchronized clocks showing the same time. Now imagine one speeds up slightly. Transferring information between them is like trying to catch a rapidly moving train. You might catch it, you might not, and if you barely catch it, it might arrive in a questionable state.

To mitigate metastability, we employ techniques like asynchronous FIFOs (First-In, First-Out) or multi-flop synchronizers. Asynchronous FIFOs use handshaking signals to transfer data between domains reliably. Multi-flop synchronizers employ multiple flip-flops in the receiving domain to increase the probability that the signal will stabilize before being used. The more flip-flops, the lower the probability of metastability propagating, but there's always a tiny risk.

In a professional setting, I've used asynchronous FIFOs for high-speed data transfers between a fast processing unit and a slower display controller, preventing data loss and ensuring accurate visual representation.

Career Expert Tips:

- Ace those interviews! Prepare effectively by reviewing the Top 50 Most Common Interview Questions on ResumeGemini.

- Navigate your job search with confidence! Explore a wide range of Career Tips on ResumeGemini. Learn about common challenges and recommendations to overcome them.

- Craft the perfect resume! Master the Art of Resume Writing with ResumeGemini's guide. Showcase your unique qualifications and achievements effectively.

- Don't miss out on holiday savings! Build your dream resume with ResumeGemini's ATS optimized templates.

Q 16. How do you optimize FPGA designs for power consumption?

Optimizing FPGA designs for power consumption involves a multi-pronged approach focusing on both architectural and implementation choices. Key strategies include:

- Clock gating: Disable clock signals to inactive components using clock gating cells. This prevents unnecessary switching activity and reduces dynamic power consumption.

- Power optimization synthesis options: Utilizing synthesis tools' power optimization options (available in Vivado, Quartus, etc.) to explore different optimization strategies. These options often involve reducing the size and complexity of logic circuits.

- Low-power libraries: Utilizing specialized libraries designed for low power consumption.

- Careful logic optimization: Minimizing logic complexity to reduce switching activity and power dissipation. This involves efficient coding practices and synthesis optimizations.

- Voltage scaling: (If supported by the FPGA) Lowering the operating voltage within the FPGA's safe limits.

- Careful selection of FPGA devices: Choosing a device family or a specific device that is optimized for low power.

For example, in a project involving a high-resolution video processing pipeline, I implemented clock gating to power down sections of the pipeline that weren't actively processing frames. This resulted in a significant reduction in overall power consumption without impacting performance. I also explored the use of Vivado's power analysis tools to find the main power culprits and focus my optimization efforts there.

Q 17. Describe your experience with various FPGA development boards.

My experience encompasses a range of FPGA development boards, including Xilinx Artix-7, Zynq-7000, and UltraScale+ devices, as well as Altera Cyclone V and Stratix 10. I'm proficient in using their respective development tools (Vivado, Quartus) for synthesis, implementation, and bitstream generation.

Each board has unique characteristics that I consider when selecting a platform for a project. For instance, the Zynq-7000's ARM processor integration is beneficial for designs requiring embedded processing, while the high-density logic available on UltraScale+ is suited for more computationally intensive tasks. The Cyclone V is more appropriate for cost-sensitive designs.

My experience extends to working with various onboard peripherals, including high-speed serial interfaces like PCIe, Ethernet, and high-speed ADCs/DACs. I'm also familiar with utilizing the onboard debugging and JTAG interfaces for thorough verification and troubleshooting of my designs.

Q 18. Explain your experience with different design methodologies (e.g., top-down, bottom-up).

I've employed both top-down and bottom-up design methodologies depending on project requirements and complexity.

Top-down design starts with a high-level architectural specification, progressively refining it into lower-level modules. This is useful for complex systems where a clear overall architecture is necessary to manage complexity. It allows for early verification of the overall design.

Bottom-up design begins with designing smaller, well-defined modules, which are then integrated to form a larger system. This is more suitable for projects where reusable components exist or where the overall architecture is less well-defined at the start. It allows for parallel development of independent modules and helps in creating a modular and maintainable design.

In practice, I often adopt a hybrid approach, combining aspects of both methodologies. For instance, in a recent project designing a network interface card, I used a top-down approach to define the overall architecture and data flow, but then employed a bottom-up approach for designing individual components like the physical layer transceiver and MAC controller, leveraging existing IP cores where possible.

Q 19. How do you handle asynchronous inputs in your designs?

Handling asynchronous inputs requires careful consideration to prevent metastability, which occurs when a signal changes state during the sampling process of a synchronous circuit. The key is to synchronise the asynchronous input with the system clock.

The most common method is using a synchronizer, which typically consists of two or more flip-flops in series. Each flip-flop reduces the probability of metastability propagating further into the system. While a single flip-flop is insufficient, multiple flip-flops significantly lessen the risk in most cases.

// Example Verilog synchronizer always @(posedge clk) begin async_sync_reg1 <= async_input; async_sync_reg2 <= async_sync_reg1; //async_sync_reg3 <= async_sync_reg2; // add more for increased robustness end

It's crucial to understand that metastability can't be entirely eliminated. The synchronizer makes it extremely improbable, but the designer should consider the timing implications and potential consequences if it does occur. Using additional logic to detect potential metastability and handle it gracefully is sometimes also done. For example, using a pulse detector or a timeout circuit to signal failures.

In my professional experience, I've used synchronizers to interface a system with external push-buttons, where the button press is an asynchronous event. This approach prevents spurious signals from affecting the system's operation.

Q 20. Explain your understanding of Finite State Machines (FSMs).

A Finite State Machine (FSM) is a sequential circuit that transitions between a finite number of states based on input signals and its current state. It's a powerful and widely used design paradigm in digital systems. It is defined by a set of states, inputs, outputs, transitions between states, and actions associated with each state or transition.

FSMs can be implemented using either Mealy or Moore models. In a Mealy machine, the output depends on both the current state and the current input, whereas in a Moore machine, the output depends solely on the current state. The choice between the two depends on the specific design requirements.

FSMs are extremely useful for controlling sequential processes and implementing complex logic. For example, in a communication protocol, an FSM might be used to manage the various phases of data transmission. In an industrial controller, it might control the sequence of operations in a manufacturing process.

When designing FSMs, it's essential to carefully define the state diagram, ensuring all possible input combinations and state transitions are accounted for. Tools like state machine editors or automated synthesis tools can significantly assist in this process.

Q 21. How would you implement a pipelined design?

Pipelining is a powerful technique for improving the throughput of a design by dividing a large computation into smaller stages, allowing multiple computations to be processed concurrently. Think of it like an assembly line; each stage performs a portion of the task, and the result is passed to the next stage.

Implementing a pipelined design involves breaking down the original sequential process into several stages, each clocked independently. Registers are inserted between the stages to hold intermediate results. This allows each stage to process a new data element while the previous data element is being processed in the subsequent stage.

// Example Verilog pipelined adder always @(posedge clk) begin stage1_reg <= a + b; stage2_reg <= stage1_reg + c; sum <= stage2_reg; end

The benefits of pipelining include increased throughput and improved performance. However, it increases the latency (the time it takes for a single data element to complete processing). The choice of pipeline stages involves balancing throughput improvement with latency.

In professional settings, I’ve utilized pipelining in high-throughput signal processing algorithms to significantly improve performance, particularly in applications requiring real-time data processing such as digital image processing or high-speed data communication.

Q 22. What are different types of memory in FPGA (e.g., Block RAM, distributed RAM)?

FPGAs offer various memory resources crucial for efficient design. The primary types are Block RAM (BRAM) and Distributed RAM (LUT RAM).

Block RAM (BRAM): BRAMs are dedicated, high-speed memory blocks integrated directly onto the FPGA fabric. They provide significant bandwidth and are optimized for fast read/write operations. Think of them as highly efficient, pre-built memory chips embedded within the FPGA. Their size varies depending on the FPGA architecture; for example, a Xilinx device might offer 18Kb or 36Kb BRAM blocks. They're ideal for applications requiring large, fast memory access, such as buffering video streams, implementing large FIFOs, or storing look-up tables.

Distributed RAM (LUT RAM): Distributed RAM leverages the FPGA's Look-Up Tables (LUTs), which are the fundamental logic elements. These LUTs can be configured to store small amounts of data, creating a distributed memory resource. Imagine it like using many tiny, individual memory cells spread throughout the FPGA. This approach is flexible but usually slower and less efficient than BRAM for larger memory needs. It's well-suited for smaller memories or when BRAM resources are exhausted, particularly when the memory access pattern isn't strictly sequential. It's commonly used to create small registers or caches.

Choosing between BRAM and LUT RAM depends on the application's memory requirements, speed needs, and available resources. If you need fast access to a large amount of data, BRAM is the clear winner. However, for smaller, less performance-critical memory elements, LUT RAM offers a flexible alternative.

Q 23. Describe your experience with formal verification techniques.

My experience with formal verification spans several projects, primarily utilizing tools like ModelSim and QuestaSim. I've employed both property-based and equivalence checking methods. In one project involving a complex packet processor, I used SystemVerilog Assertions (SVA) to formally verify the design's compliance with the communication protocol specification. This involved defining properties to capture the expected behavior, such as data integrity and sequencing. The formal verification tool then exhaustively checked the design against these properties, identifying subtle bugs that would have been extremely difficult to find with traditional simulation-based testing. The process greatly enhanced our confidence in the design's correctness and significantly reduced the risk of costly field failures.

Another project involved equivalence checking between a high-level, RTL design and a lower-level, optimized implementation. This ensured that the optimization process didn't introduce unintended behavioral changes. Formal verification here played a vital role in demonstrating that the optimized version remained functionally equivalent to the original.

Q 24. Explain your understanding of different coding styles for VHDL/Verilog.

Coding styles in VHDL and Verilog vary significantly, impacting readability and maintainability. In VHDL, I prefer a structured style with well-defined entities, architectures, and packages. This enhances modularity and reusability. I favour descriptive naming conventions for signals and components. For instance, instead of signal a : std_logic; I'd use signal data_in : std_logic;. This increases clarity. I also make extensive use of VHDL's data types to improve clarity and prevent common coding errors.

In Verilog, a similar approach is taken, but the style leans towards a more concise and procedural approach. I emphasize clear module definitions, consistent indentation, and the use of named parameters to improve code readability. I avoid excessive use of implicit wire declarations to prevent accidental signal connections. Instead I explicitly declare all signals. The use of parameterized modules is crucial for creating reusable and flexible code. For example, a parameterized FIFO module can handle various data widths and depths. module fifo #(parameter DATA_WIDTH=8, DEPTH=64) ( ... );

Furthermore, a combination of both styles can be used – particularly when working with projects that utilise existing libraries or code from others. The core philosophy across both languages remains consistent: Prioritize clarity, modularity, and ease of understanding.

Q 25. How do you ensure code readability and maintainability?

Ensuring code readability and maintainability is paramount for long-term success. My approach involves several key strategies:

Consistent coding style: Adhering to a well-defined coding standard (e.g., using a style guide enforced by linters) ensures uniformity across the project.

Meaningful naming conventions: Signals, variables, and components should have descriptive names that clearly indicate their purpose. For example,

counter_valueis much better thancnt.Modular design: Breaking down complex designs into smaller, manageable modules promotes reusability and reduces complexity. This improves maintainability significantly.

Comprehensive commenting: Well-written comments explain the purpose, functionality, and design choices within the code. I avoid comments that merely restate the obvious code.

Version control: Using a version control system (like Git) allows for tracking changes, collaboration, and easy rollback to previous versions if necessary.

Code reviews: Regular code reviews by peers help identify potential issues and ensure adherence to coding standards.

These practices are not just good habits but essential for efficient design, collaboration, and the long-term success of any FPGA project.

Q 26. What are your experiences with different constraints languages (e.g., XDC)?

My experience with constraint languages primarily revolves around XDC (eXtensible Configuration Description). XDC is a powerful language that enables precise control over the physical implementation of the FPGA design. I've used XDC extensively to:

Specify clock constraints: Defining clock periods, jitter, and uncertainty is crucial for timing closure. XDC allows me to specify these parameters accurately, leading to reliable high-frequency designs.

Assign input/output pins: This is essential to map design signals to specific FPGA pins based on the board's physical layout.

Control routing resources: While the synthesis and place and route tools usually perform well, sometimes manual intervention is required. XDC allows for that control, to achieve better timing or routing performance, or to handle special cases.

Manage physical constraints: XDC can be used to enforce various physical constraints, such as setting the location of specific logic blocks or managing signal routing preferences, potentially improving signal integrity and performance.

Understanding XDC is critical for ensuring that the FPGA design meets timing requirements and integrates seamlessly with the target hardware. Without proper constraints, the synthesis and place and route tools may not produce an optimal or even functional implementation.

Q 27. Describe a challenging FPGA design project and how you overcame the difficulties.

One particularly challenging project involved designing a high-speed data acquisition system for a scientific instrument. The design had extremely tight timing constraints and required processing a massive data stream with very low latency. The initial implementation, while functionally correct, failed to meet the timing closure requirements. The critical path was dominated by a complex data processing block.

To overcome this, I employed a multi-pronged approach:

Pipeline Optimization: I restructured the data processing block to be pipelined, breaking it into smaller stages to reduce the critical path delay. This improved the clock frequency and satisfied the timing constraints.

Resource Optimization: Careful analysis of the resource utilization revealed unnecessary logic and memory usage. By optimizing the algorithms and data structures, I freed up critical resources and improved the design's timing performance.

Constraint Refinement: I systematically refined the XDC constraints, adjusting the clock specifications and adding additional constraints to guide the placement and routing tools toward better solutions. I worked closely with the physical design team for efficient resource utilization.

Advanced Synthesis techniques: Implementing techniques like register balancing and aggressive pipelining helped further optimize the timing characteristics.

Through this iterative process of design optimization, constraint refinement, and close collaboration, we successfully met all timing requirements and delivered a functioning high-speed data acquisition system. This project highlighted the importance of thorough planning, systematic problem-solving, and the strategic use of advanced FPGA design techniques.

Key Topics to Learn for VHDL and Verilog for FPGA Programming Interviews

- Data Types and Operators: Understand the intricacies of different data types (std_logic, signed, unsigned, etc.) and their corresponding operators in both VHDL and Verilog. Practice converting between them and optimizing for efficient FPGA implementation.

- Sequential and Combinational Logic: Master the design and implementation of both sequential (using flip-flops, registers) and combinational (using logic gates, multiplexers) circuits. Be prepared to discuss timing considerations and optimization strategies.

- Behavioral Modeling: Develop a strong understanding of behavioral modeling techniques to describe the functionality of your designs at a higher level of abstraction. This includes using processes, always blocks, and case statements effectively.

- Structural Modeling: Learn how to model your design using structural descriptions, connecting individual components to create a larger system. This is crucial for understanding hierarchical design and complex FPGA projects.

- Finite State Machines (FSMs): Design, implement, and analyze FSMs using both VHDL and Verilog. Be ready to discuss different FSM encoding styles (one-hot, binary) and their trade-offs.

- Memory and Interface Design: Gain practical experience working with various memory types (RAM, ROM) and interfaces (e.g., AXI, Avalon) commonly used in FPGA designs. Understand timing constraints and data flow.

- Testbenches and Simulation: Develop effective testbenches to verify the functionality of your designs. Understand the simulation process and debugging techniques using common simulators (ModelSim, Vivado Simulator).

- Synthesis and Implementation: Familiarize yourself with the synthesis and implementation process for FPGAs, including constraint definition (timing constraints, physical constraints) and understanding the resulting resource utilization.

- Advanced Topics (Optional but Beneficial): Explore concepts like pipelining, clock domain crossing, and asynchronous design techniques. These often differentiate top candidates.

Next Steps

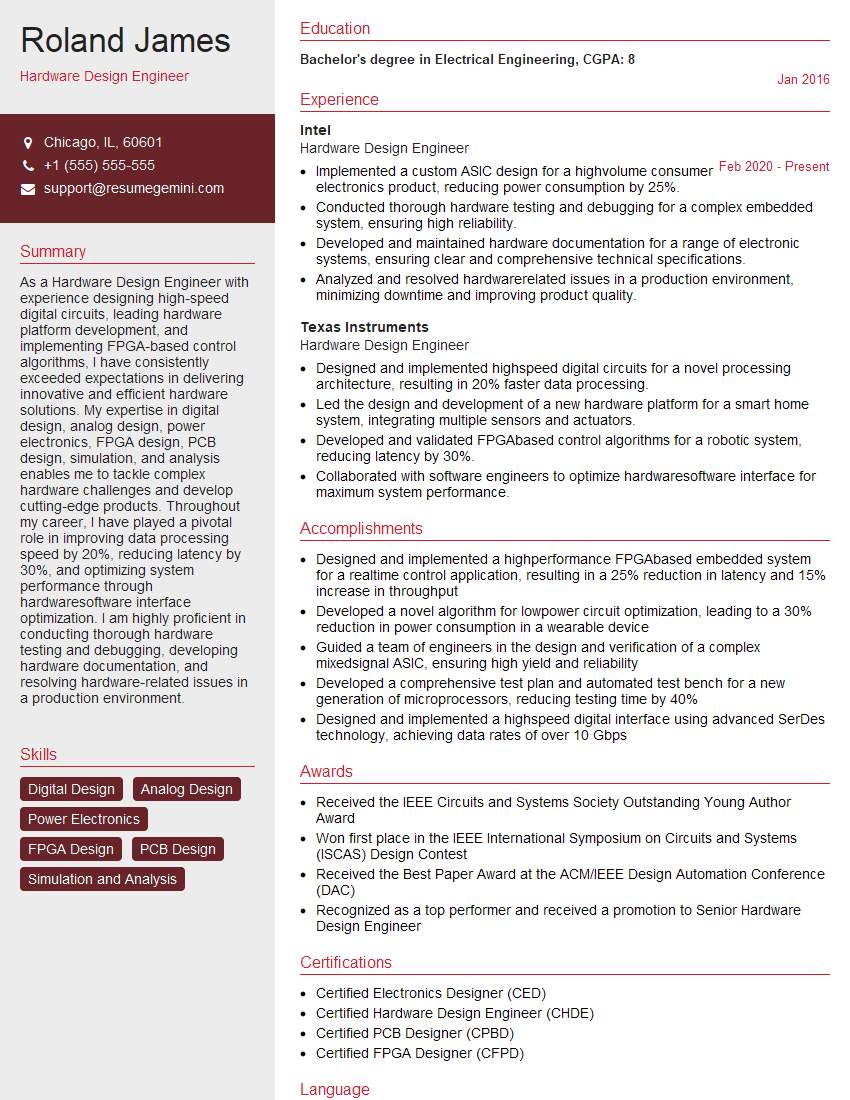

Mastering VHDL and Verilog for FPGA programming opens doors to exciting career opportunities in various fields like embedded systems, high-performance computing, and digital signal processing. To maximize your job prospects, a well-crafted resume is crucial. An ATS-friendly resume, optimized for Applicant Tracking Systems, significantly increases the chances of your application being seen by recruiters. ResumeGemini is a trusted resource to help you create a professional and impactful resume tailored to your skills and experience. Examples of resumes tailored to VHDL and Verilog for FPGA Programming are available to help guide you in building your own.

Explore more articles

Users Rating of Our Blogs

Share Your Experience

We value your feedback! Please rate our content and share your thoughts (optional).

What Readers Say About Our Blog

Hello,

we currently offer a complimentary backlink and URL indexing test for search engine optimization professionals.

You can get complimentary indexing credits to test how link discovery works in practice.

No credit card is required and there is no recurring fee.

You can find details here:

https://wikipedia-backlinks.com/indexing/

Regards

NICE RESPONSE TO Q & A

hi

The aim of this message is regarding an unclaimed deposit of a deceased nationale that bears the same name as you. You are not relate to him as there are millions of people answering the names across around the world. But i will use my position to influence the release of the deposit to you for our mutual benefit.

Respond for full details and how to claim the deposit. This is 100% risk free. Send hello to my email id: [email protected]

Luka Chachibaialuka

Hey interviewgemini.com, just wanted to follow up on my last email.

We just launched Call the Monster, an parenting app that lets you summon friendly ‘monsters’ kids actually listen to.

We’re also running a giveaway for everyone who downloads the app. Since it’s brand new, there aren’t many users yet, which means you’ve got a much better chance of winning some great prizes.

You can check it out here: https://bit.ly/callamonsterapp

Or follow us on Instagram: https://www.instagram.com/callamonsterapp

Thanks,

Ryan

CEO – Call the Monster App

Hey interviewgemini.com, I saw your website and love your approach.

I just want this to look like spam email, but want to share something important to you. We just launched Call the Monster, a parenting app that lets you summon friendly ‘monsters’ kids actually listen to.

Parents are loving it for calming chaos before bedtime. Thought you might want to try it: https://bit.ly/callamonsterapp or just follow our fun monster lore on Instagram: https://www.instagram.com/callamonsterapp

Thanks,

Ryan

CEO – Call A Monster APP

To the interviewgemini.com Owner.

Dear interviewgemini.com Webmaster!

Hi interviewgemini.com Webmaster!

Dear interviewgemini.com Webmaster!

excellent

Hello,

We found issues with your domain’s email setup that may be sending your messages to spam or blocking them completely. InboxShield Mini shows you how to fix it in minutes — no tech skills required.

Scan your domain now for details: https://inboxshield-mini.com/

— Adam @ InboxShield Mini

Reply STOP to unsubscribe

Hi, are you owner of interviewgemini.com? What if I told you I could help you find extra time in your schedule, reconnect with leads you didn’t even realize you missed, and bring in more “I want to work with you” conversations, without increasing your ad spend or hiring a full-time employee?

All with a flexible, budget-friendly service that could easily pay for itself. Sounds good?

Would it be nice to jump on a quick 10-minute call so I can show you exactly how we make this work?

Best,

Hapei

Marketing Director

Hey, I know you’re the owner of interviewgemini.com. I’ll be quick.

Fundraising for your business is tough and time-consuming. We make it easier by guaranteeing two private investor meetings each month, for six months. No demos, no pitch events – just direct introductions to active investors matched to your startup.

If youR17;re raising, this could help you build real momentum. Want me to send more info?

Hi, I represent an SEO company that specialises in getting you AI citations and higher rankings on Google. I’d like to offer you a 100% free SEO audit for your website. Would you be interested?

Hi, I represent an SEO company that specialises in getting you AI citations and higher rankings on Google. I’d like to offer you a 100% free SEO audit for your website. Would you be interested?

good